ECE 576 - Homework Assignment 5 (Extra Credit: 20 Points)

Due End of Semester via Demo to Instructor

Announcements and Clarifications:

Power Analysis

In this assignment, you will extend the approximate timed system developed in HW Assignment 2 to incorporate power state machines for various system components to analyze the total system performance and power consumption. The revised system model should consider using the XScale processor which has a maximum clock frequency of 624 MHz. The system bus, memory, and hardware coprocessors will continue to operate at 100 MHz.

Assuming a latency constraint equivalent to the orignal implementation (i.e. 8193437 cycles at 100 MHz = 81.9 ms), determine the lowest frequency the XScale processor can operate at to meet this constraint and the resulting power consumption.

The following provides the power state machines that were developed in lecture for the XScale processor, memory, and hardware accelerators that should be utilized within this assignment. Each power state machines should be implemented as separate SystemC modules with an appropriate interface supporting methods for indicting the vents that result in changes in power states. Hint: This interface can be implemented generically for all power state machines.'

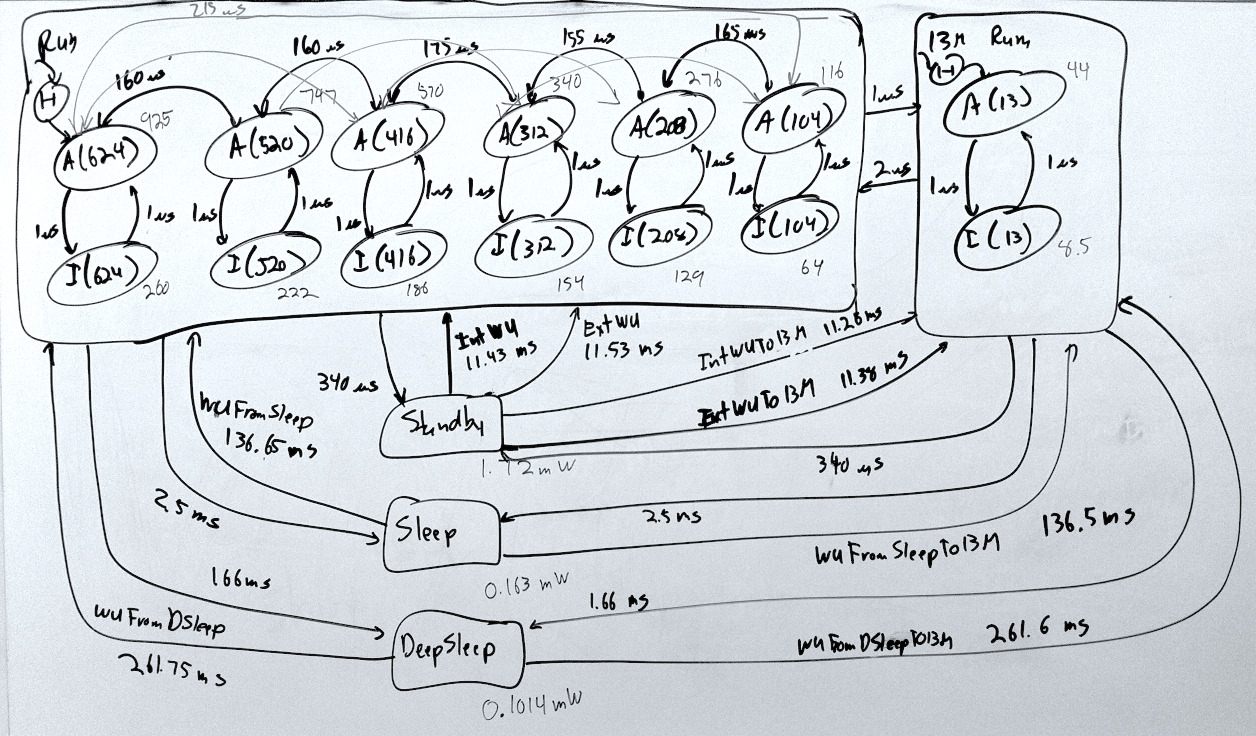

Power State Machines for SW (Microprocessor)

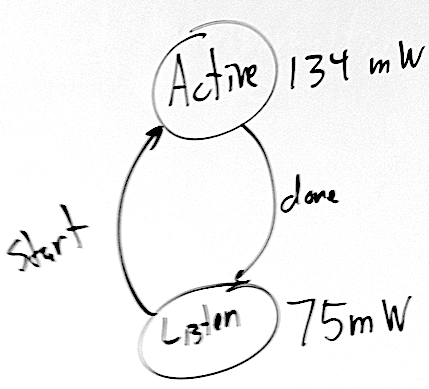

Power State Machines for Matrix Multiply Accelerator

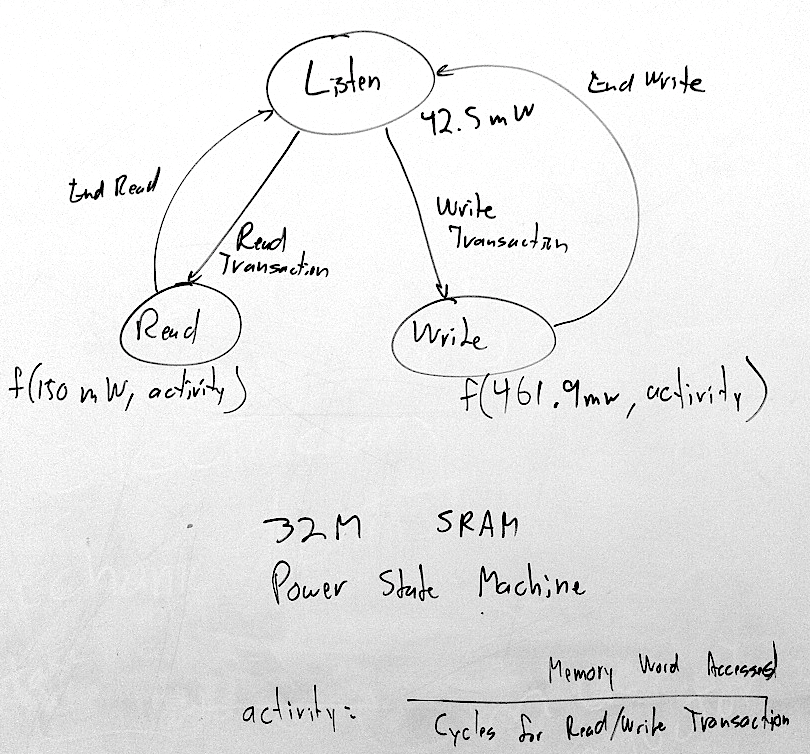

Power State Machines for Memory

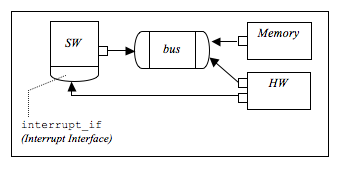

Analysis of Busy Waiting versus Interrupts for Hardware/Software Synchronization

In the original system implementation shown below, busy waiting was utilized to synchronize between the software and hardware components implementing the matrix multiplication operation. Modify this implementation to utilize an interrupt driven interface for synchronization between the hardware coprocessor and XScale processors as shown below.

Determine if low-power idle of standby modes of the XScale processor can be utilized to reduce the system power consumption assuming the same overall system latency constraint (i.e. 8193437 cycles at 100 MHz = 81.9 ms). If so, determine the system configuration that yields the lowest power consumption while meeting the latency constraint.