## PRACTICE PROBLEMS SET 1 Digital Logic and Introductory Review Problems

- 1. Design a circuit that computes F = 5A, using the fewest number of 4-bit adders. Input A is a 4-bit number. How many bits are required for the result to avoid overflow?

- 2. Design a 3-bit ALU to perform the operations specified. Draw the internal components and connections within each AL-extender, however you can use a block diagram to depict the adder.

| Inputs |   | Operation       |

|--------|---|-----------------|

| а      | b | Operation       |

| 0      | 0 | Set output to 2 |

| 0      | 1 | A – B           |

| 1      | 0 | B + 1           |

| 1      | 1 | A + B           |

- 3. Create the internal design of a full subtractor. Be sure to include a truth table, logic equations, and a gate-level schematic.

- 4. Using only 2-input, 1-output MUXes, implement the following components

- a) 8-input, 1 output MUX

- b) 2-input AND gate

- c) half adder

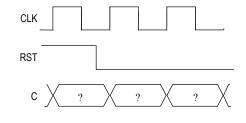

- 5. Trace the behavior of the Verilog code provided. Fill in the value of C in each time step. (*Hint: run the code through the simulator to verify your result*)

| always @ (posedge RST or posedge CLK) begin |           |

|---------------------------------------------|-----------|

| if( RST == 1 ) begin                        |           |

| A = 2; B = 4; C = 1;                        |           |

| end                                         |           |

| else begin                                  |           |

| A <= B;                                     |           |

| B = B + 1;                                  |           |

| C <= A+ B;                                  |           |

| end                                         |           |

| end                                         |           |

|                                             | $\square$ |

- 6. Provide an example/scenario where blocking statements are useful.

- 7. Provide an example/scenario where non-blocking statements are useful.

- According to the Mythical Man Month, designer productivity decreases due to team-size complexity. Assuming a hypothetical 6,000,000 transistor project (T), in which a single designer working alone can produce 7,500 transistors per months (P), and each additional designer added to project results in a productivity decrease of 150 transistors per designer (D).

- a) Derive an equation to compute the months until completion (M) based on T, P, D, and N (team size).

- b) Plot the months until completion (M) verses team size (N), with the team size ranging from 1 designer to 50 designers. *Hint:* use excel or similar program to plot graph.

- c) Plot the productivity per designer (I) verses team size (N), with the team size ranging from 1 designer to 50 designers.

- d) What is the optimal team size?

- e) If D = 200, what is the optimal team size?

- 9. If specifying functionality at a higher level of abstraction increases productivity, what would be the benefit of specifying an module/application at the structural level?