## Xilinx ISE 11.1 Simulation Tutorial

This tutorial provides a step-by-step guide to simulating a Verilog description of a 2-input AND gate using Xilinx ISE 11.1 – 11.4.

- 1. Start Xilinx ISE Project Navigator

- 2. Create a new project

- Click on File, then choose New Project on the drop down menu

- Enter your project name, in this case the project is called "AND2gate"

- Choose your project location, this project is stored at "Z:\Projects\AND2gate"

- Leave the working directory entry blank.

- Choose HDL as the source type from the Top-Level Source Type menu.

- Click Next button

| 📧 New Project Wizard 🛛 🔀                  |                                                     |        |  |  |  |  |  |  |  |  |

|-------------------------------------------|-----------------------------------------------------|--------|--|--|--|--|--|--|--|--|

| Create New Project<br>Specify project loo |                                                     |        |  |  |  |  |  |  |  |  |

| Enter a name, locati                      | ions, and comment for the project                   |        |  |  |  |  |  |  |  |  |

| Name:                                     | And2gate                                            |        |  |  |  |  |  |  |  |  |

| Location:                                 | C:\Temp\Projects\And2gate                           |        |  |  |  |  |  |  |  |  |

| Working Directory:                        |                                                     |        |  |  |  |  |  |  |  |  |

| Description:                              |                                                     |        |  |  |  |  |  |  |  |  |

|                                           |                                                     |        |  |  |  |  |  |  |  |  |

|                                           |                                                     |        |  |  |  |  |  |  |  |  |

|                                           |                                                     |        |  |  |  |  |  |  |  |  |

|                                           |                                                     |        |  |  |  |  |  |  |  |  |

|                                           |                                                     |        |  |  |  |  |  |  |  |  |

|                                           |                                                     |        |  |  |  |  |  |  |  |  |

|                                           |                                                     |        |  |  |  |  |  |  |  |  |

| - Select the type of to                   | Select the type of top-level source for the project |        |  |  |  |  |  |  |  |  |

| Top-level source typ                      |                                                     |        |  |  |  |  |  |  |  |  |

| HDL                                       |                                                     |        |  |  |  |  |  |  |  |  |

|                                           |                                                     |        |  |  |  |  |  |  |  |  |

|                                           |                                                     |        |  |  |  |  |  |  |  |  |

| More Info                                 | Next >                                              | Cancel |  |  |  |  |  |  |  |  |

- 3. You will be asked to select the hardware and design flow for this project.

- For *Family*, choose *Spartan3E*

- For *Device*, choose *XC3S500E*

- For *Package*, choose *FG320*

- For *Speed*, choose -4

- For *Simulator*, choose *ISim (VHDL/Verilog)*

- Click Next button

| elect the device and design flow for the | Value                         |   |

|------------------------------------------|-------------------------------|---|

| Property Name<br>Product Category        |                               | ~ |

| Family                                   | Spartan3E                     | ~ |

| ramiy<br>Device                          | xC35500E                      | ~ |

| Package                                  | FG320                         |   |

| Speed                                    | -4                            | * |

| Top-Level Source Type                    | HDL                           | ~ |

| Synthesis Tool                           | XST (VHDL/Verilog)            | ~ |

| Simulator                                | ISim (VHDL/Verilog)           | ~ |

| Preferred Language                       | Verilog                       | ~ |

| Property Specification in Project File   | Store non-default values only | ~ |

| Manual Compile Order                     |                               |   |

| Enable Enhanced Design Summary           |                               |   |

| Enable Message Filtering                 |                               |   |

| Display Incremental Messages             |                               |   |

4. Next you are asked if you want to create new source files. We'll add source files later so just click on the *Next* button.

| additional s    | tionally create one source at this time. You<br>ources with the "Project->New Source" co |      | : page, and later create |

|-----------------|------------------------------------------------------------------------------------------|------|--------------------------|

| Create a new so | urce                                                                                     |      |                          |

|                 | Source File                                                                              | Туре | New Source               |

| 1               |                                                                                          |      | Remove                   |

|                 |                                                                                          |      |                          |

|                 |                                                                                          |      |                          |

|                 |                                                                                          |      |                          |

|                 |                                                                                          |      |                          |

|                 |                                                                                          |      |                          |

|                 |                                                                                          |      |                          |

|                 |                                                                                          |      |                          |

|                 |                                                                                          |      |                          |

|                 |                                                                                          |      |                          |

|                 |                                                                                          |      |                          |

|                 |                                                                                          |      |                          |

|                 |                                                                                          |      |                          |

|                 |                                                                                          |      |                          |

|                 |                                                                                          |      |                          |

|                 |                                                                                          |      |                          |

5. You are asked if you want to add existing source files. Since we have a new project we don't have any existing files. Additionally, if you did have pre-existing files, you can also add these to the project later. Click on the *Next* button.

| 152 | 🖻 New Project Wizard 🛛 🛛 🔀                                                                                                                                                                               |                             |            |  |  |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------|--|--|--|--|--|--|--|

| ¢   | Add Existing Sources<br>Adding existing sources is optional. Additional sources can be added after the project is created using the "Project-<br>>Add Source" or "Project->Add Copy of Source" commands. |                             |            |  |  |  |  |  |  |  |

|     | ٨dd                                                                                                                                                                                                      | existing sources            |            |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                          | Source File Copy to Project | Add Source |  |  |  |  |  |  |  |

|     | 1                                                                                                                                                                                                        |                             | Remove     |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                          |                             |            |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                          |                             |            |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                          |                             |            |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                          |                             |            |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                          |                             |            |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                          |                             |            |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                          |                             |            |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                          |                             |            |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                          |                             |            |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                          |                             |            |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                          |                             |            |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                          |                             |            |  |  |  |  |  |  |  |

|     |                                                                                                                                                                                                          |                             |            |  |  |  |  |  |  |  |

|     | Mor                                                                                                                                                                                                      | re Info                     | Cancel     |  |  |  |  |  |  |  |

6. A project summary will appear. Click on the *Finish* button.

| 🚾 New Project Wizard                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Project Summary</b><br>Project Navigator will create a new project with the following specifications.                                                                                                    |

| Project:<br>Project Name: And2gate<br>Project Path: C:\Temp\Projects\And2gate<br>Working Directory:<br>Description:<br>Top Level Source Type: HDL                                                           |

| Device:<br>Device Family: Spartan3E<br>Device: xc3s500e<br>Package: fg320<br>Speed: -4                                                                                                                      |

| Synthesis Tool: XST (VHDL/Verilog)<br>Simulator: ISim (VHDL/Verilog)<br>Preferred Language: Verilog<br>Property Specification in Project File: Store non-default values only<br>Manual Compile Order: false |

| Enhanced Design Summary: enabled<br>Message Filtering: disabled<br>Display Incremental Messages: disabled                                                                                                   |

| More Info < Back Finish Cancel                                                                                                                                                                              |

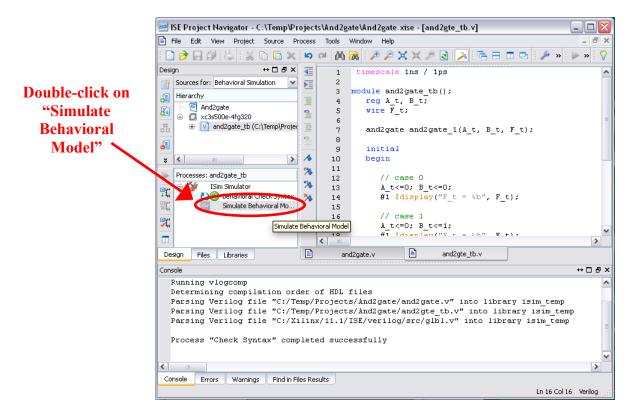

- 7. You now have a project by the name of "AND2gate". Next you want to specify the files in this project are for behavioral simulation.

- Click on the Sources for: drop down menu, choose Behavioral Simulation

| Choose                     | 🚾 IS           | E Proj              | ect N                                                        | avigator    | - C:\Ter   | np\Proj                     | ects\Ar | nd2gate\/ | nd2gat | e.xise |          |          |         | _              |         |

|----------------------------|----------------|---------------------|--------------------------------------------------------------|-------------|------------|-----------------------------|---------|-----------|--------|--------|----------|----------|---------|----------------|---------|

| <b>"Behavioral</b>         | File           | Edit                | View                                                         | Project     | Source     | Process                     | Tools   | Window    | Help   |        |          |          |         |                |         |

| "Behavioral<br>Simulation" | Desigr         | Sources<br>Hierarch | for B<br>ny<br>And2g<br>xc3s5l<br>No<br>Ne<br>Ne<br>Ie desig | ehavioral S | iimulation | ₽×<br>•<br>•<br>•<br>•<br>• |         |           |        | XX     | <i>P</i> | <u>-</u> | I 📭 🔢 🖋 | * » : <b>)</b> | >> 😯    |

|                            | Consc<br>Consc | le                  | Files                                                        | Libraries   |            | nd in Files                 |         |           |        |        |          |          |         | +              | • = # × |

|                            |                |                     |                                                              |             |            |                             |         |           |        |        |          |          |         |                |         |

- 8. Now we want to add a new file to our project.

- Click on *Project*, choose *New Source*

- Choose *Verilog Module* as the file type

- In the *File name*: box enter the desired file name, in this case the file is named "and2gate.v"

- Click on the *Next* button

| 🖻 New Source Wizard 🛛 🔀                                                                                                                                                                                                                                            |                                                                    |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|--|--|--|

| Select Source Type<br>Select source type, file name and its location.                                                                                                                                                                                              |                                                                    |  |  |  |  |  |  |  |

| <ul> <li>IP (CORE Generator &amp; Architecture Wizard)</li> <li>Schematic</li> <li>User Document</li> <li>Verliog Module</li> <li>Verliog Test Fixture</li> <li>VHDL Library</li> <li>VHDL Package</li> <li>VHDL Test Bench</li> <li>Embedded Processor</li> </ul> | File name:<br>and2gate.v<br>Location:<br>C:\Temp\Projects\And2gate |  |  |  |  |  |  |  |

| More Info                                                                                                                                                                                                                                                          | Next > Cancel                                                      |  |  |  |  |  |  |  |

9. You will be asked for the module's port names/types. You can skip this step and click on the *Next* button.

| Define Moo<br>Specify | dule<br>ports for module. |          |   |     |     |     |   |

|-----------------------|---------------------------|----------|---|-----|-----|-----|---|

| 1odule name           | and2gate                  |          |   |     |     |     |   |

|                       | Port Name                 | Directio | n | Bus | MSB | LSB |   |

|                       |                           | input    | ~ |     |     |     |   |

|                       |                           | input    | ~ |     |     |     |   |

|                       |                           | input    | ~ |     |     |     |   |

|                       |                           | input    | ~ |     |     |     |   |

|                       |                           | input    | ~ |     |     |     |   |

|                       |                           | input    | ~ |     |     |     |   |

|                       |                           | input    | ~ |     |     |     |   |

|                       |                           | input    | ~ |     |     |     |   |

|                       |                           | input    | ~ |     |     |     |   |

|                       |                           | input    | ~ |     |     |     |   |

|                       |                           | input    | ~ |     |     |     |   |

|                       |                           | input    | ~ |     |     |     | - |

|                       |                           |          |   |     |     |     |   |

10. A project summary will appear. Click on the Finish button.

| 📧 New Source Wizard                                                                                                                                                        | ×                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Summary<br>Project Navigator will create a new skeleton source wit                                                                                                         | h the following specifications. |

| Add to Project: Yes<br>Source Directory: C:\Temp\Projects\And2gate<br>Source Type: Verilog Module<br>Source Name: and2gate.v<br>Module name: and2gate<br>Port Definitions: |                                 |

| More Info                                                                                                                                                                  | < Back Finish Cancel            |

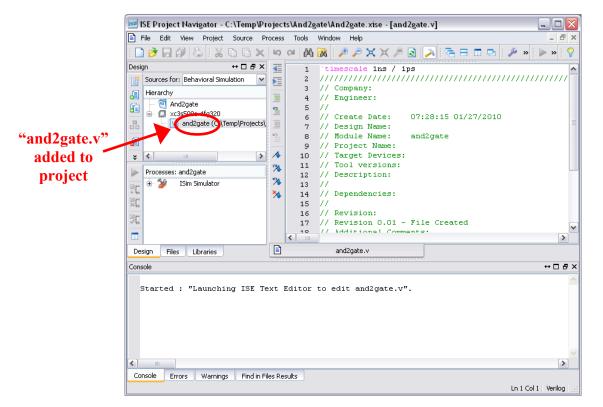

11. The "and2gate.v" file has been added to your project.

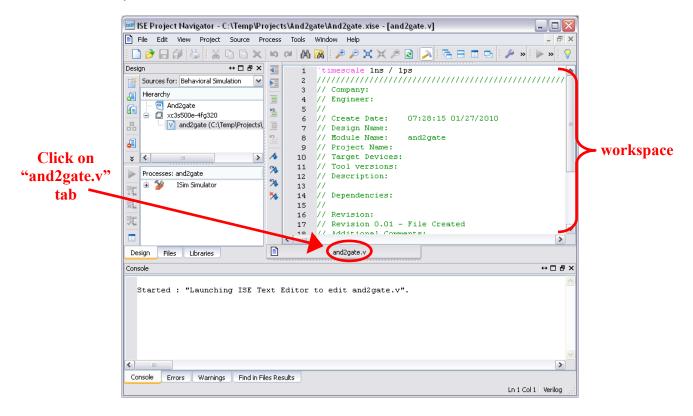

12. Click on the and2gate.v tab to show the file contents. You are now ready to specify the and2gate module's functionality.

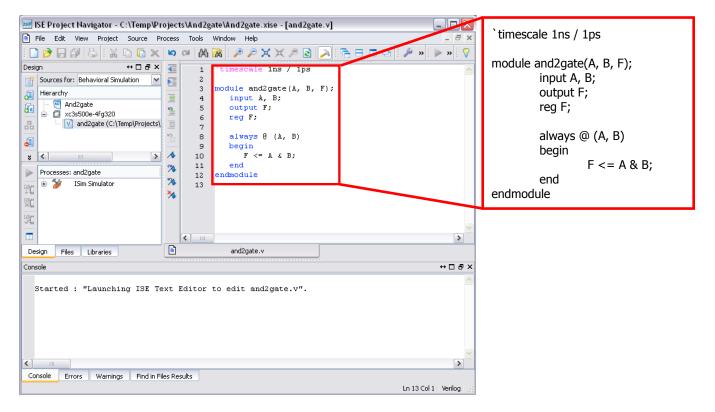

- 13. Notice that the ISE has already entered a comments sections along with a couple of lines of code for us.

- The line "`timescale 1ns/ 1ps" is located at the top of the file. The Verilog language uses dimensionless time units, and these time units are mapped to "real" time units within the simulator. `timescale is used to map to the "real" time values using the statement `timescale <time1> / <time2>, where <time1> indicates the time units associated with the #delay values, and the <time2> indicates the minimum step time used by the simulator.

- The and2gate module is also declared using "module and2gate();" and "endmodule", but the ports are left for us to define.

- We finish specifying the functionality of the and2gate module as shown below.

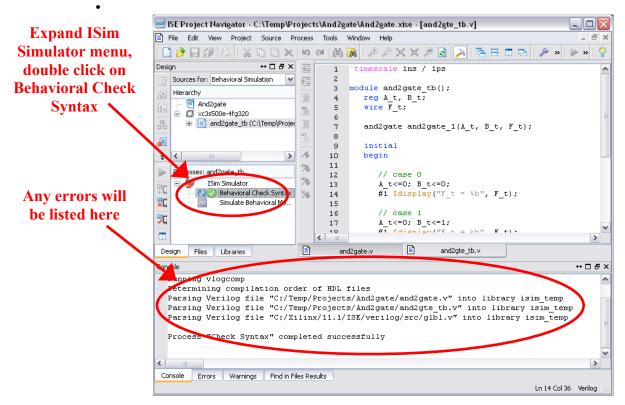

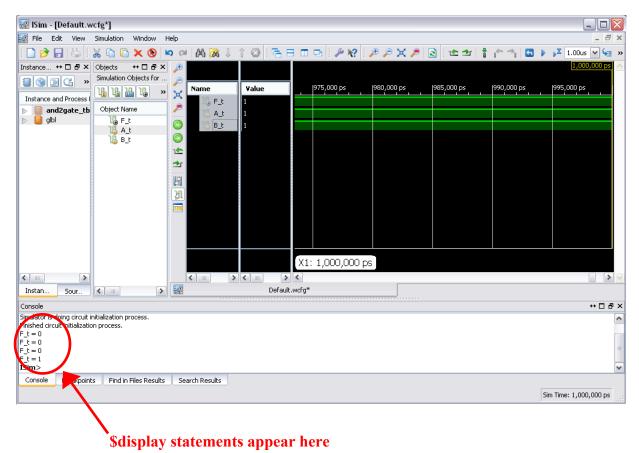

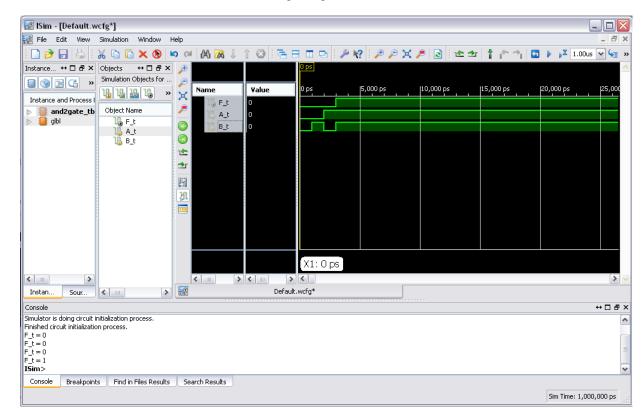

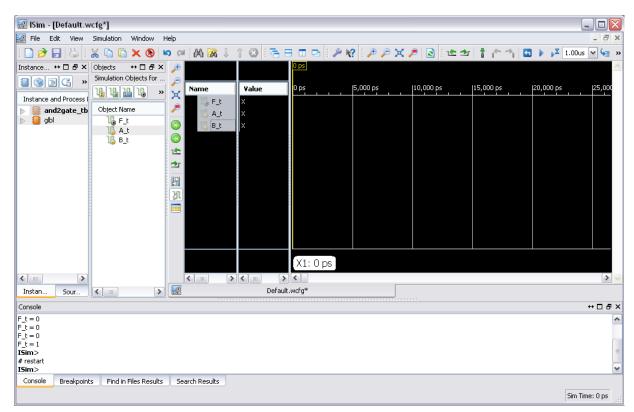

14. We also want to add a test bench and again follow Steps 8 – 11 to add "and2gate\_tb.v". Then we add the functionality of the testbench module as shown below.

| 🚾 ISE Project Navigator - C:\Temp\Pr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | `timescale 1ns / 1ps |          |                                                       |                                       |                                                        |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------|-------------------------------------------------------|---------------------------------------|--------------------------------------------------------|--|--|--|

| File Edit View Project Source Process Tools Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |          |                                                       |                                       |                                                        |  |  |  |

| i 🗋 🆻 🗐 🕼 🕌 i 🐰 🗅 🗳 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5                    | ⊲ M      | 🕅 : 🎤 🔎 🗙 🗶 🔎 💽 🥕 🖻 🗖 🖻                               | 🗄 🔑 🗴 : 🕨 : 📎                         | module and2gate_tb();                                  |  |  |  |

| Design ↔ □ ₽ ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>4</b> E           | 1        | `timescale 1ns / 1ps                                  | <b>^</b>                              | reg A_t, B_t;                                          |  |  |  |

| Sources for: Behavioral Simulation 💌                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ÞE                   | 2        | <pre>module and2gate tb();</pre>                      |                                       | wire F t;                                              |  |  |  |

| Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      | 4        | reg A t, B t;                                         |                                       |                                                        |  |  |  |

| Image: Image | 2                    | 5        | wire F_t;                                             |                                       | and2gate and2gate_1(A_t, B_t, F_t);                    |  |  |  |

| and2gate_tb (C:\Temp\Projec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      | 6        | and2gate and2gate $1(A t, B t, F t)$                  |                                       |                                                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                    | 8        | analyase analyase_r(n_s, b_s, r_s,                    | ,                                     | 1-11-1                                                 |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      | 9        | initial                                               |                                       | initial                                                |  |  |  |

| * <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A                    | 10<br>11 | begin                                                 |                                       | begin                                                  |  |  |  |

| Processes: and2gate_tb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | *                    | 12       | // case 0                                             |                                       |                                                        |  |  |  |

| 🛒 🕀 🎾 ISim Simulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | *                    | 13       | A_t<=0; B_t<=0;<br>#1 \$display("F t = %b", F t);     |                                       | // case 0                                              |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | *                    | 14<br>15 | #1 \$display("r_t = \$b", r_t);                       |                                       | A t<=0; B t<=0;                                        |  |  |  |

| St.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | 16       | // case 1                                             |                                       | $\#1$ \$display("F_t = %b", F_t);                      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      | 17       | $A_t <= 0; B_t <= 1;$ $#1 Sdienler("E t = 2b", E t);$ | ~                                     |                                                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      | <        |                                                       | >                                     | // case 1                                              |  |  |  |

| Design Files Libraries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      | ar       | nd2gate.v 📄 and2gte_tb.v                              |                                       | A t<=0; B t<=1;                                        |  |  |  |

| Console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |          |                                                       | ↔□♂×                                  | , ,                                                    |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |          |                                                       | <u>~</u>                              | #1 \$display("F_t = %b", F_t);                         |  |  |  |

| Started : "Launching ISE Te                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xt                   | Editor   | to edit and2gate.v".                                  |                                       |                                                        |  |  |  |

| Started : "Launching ISE Te                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xt                   | Editor   | to edit and2gte_tb.v".                                |                                       | // case 2                                              |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |          |                                                       |                                       | A_t<=1; B_t<=0;                                        |  |  |  |

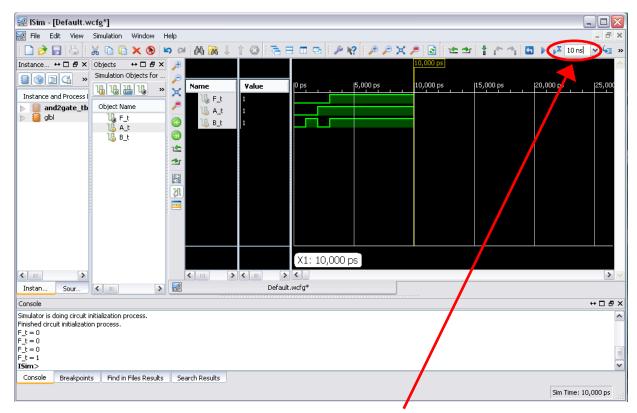

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |          |                                                       |                                       | #1 \$display("F_t = %b", F_t);                         |  |  |  |