## Sequential Logic Design D Flip-Flop

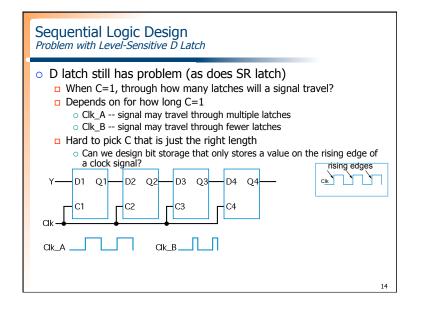

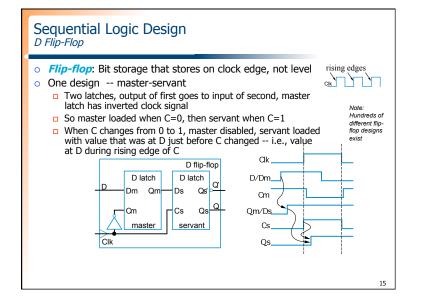

- $\,\circ\,$  Solves problem of not knowing through how many latches a signal travels when C=1

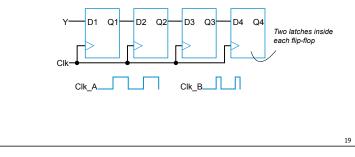

- $\hfill\square$  In figure below, signal travels through exactly one flip-flop, for Clk\_A or Clk\_B

- Why? Because on rising edge of Clk, all four flip-flops are loaded simultaneously -- then all four no longer pay attention to their input, until the next rising edge. Doesn't matter how long Clk is 1.

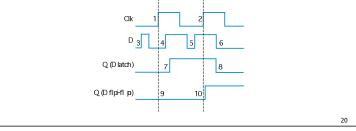

## Sequential Logic Design D Latch vs. D Flip-Flop

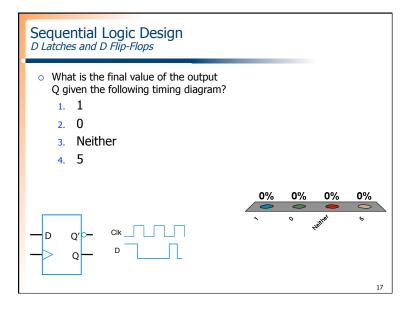

- Latch is level-sensitive: Stores D when C=1

- Flip-flop is edge triggered: Stores D when C changes from 0 to 1

- Saying "level-sensitive latch," or "edge-triggered flip-flop," is redundant

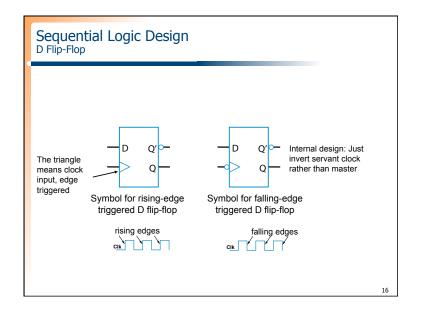

- □ Two types of flip-flops -- rising or falling edge triggered.

- Comparing behavior of latch and flip-flop: