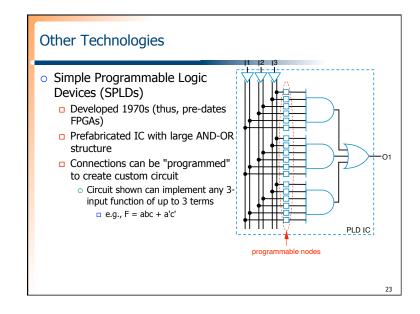

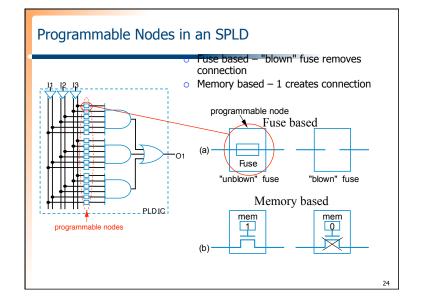

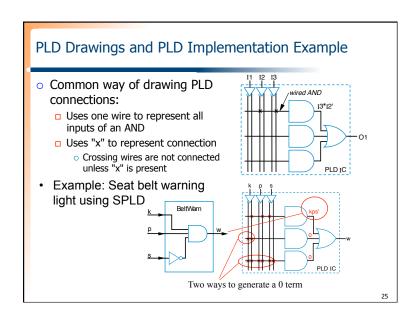

## More on PLDs Originally (1970s) known as Programmable Logic Array – PLA Had programmable AND and OR arrays AMD created "Programmable Array Logic" - "PAL" (trademark) Only AND array was programmable (fuse based) Lattice Semiconductor Corp. created "Generic Array Logic – "GAL" (trademark) Memory based o As IC capacities increased, companies put multiple PLD structures on one chip, interconnecting them □ Become known as Complex PLDs (CPLD), and older PLDs became known as Simple PLDs (SPLD) o GENERALLY SPEAKING, difference of SPLDs vs. CPLDs vs. FPGAs: □ SPLD: tens to hundreds of gates, and usually non-volatile (saves bits without power) □ CPLD: thousands of gates, and usually non-volatile □ FPGA: tens of thousands of gates and more, and usually volatile (but no reason why couldn't be non-volatile)

26