# ECE 274 Digital Logic

RTL Design – Determining Clock Frequency and Behavioral RTL Design: C-to-Gates

Digital Design 5.4 – 5.5

# Digital Design Chapter 5: RTL Design Slides to accompany the textbook Digital Design, First Edition, by Frank Vahid, John Wiley and Sons Publishers, 2007. http://www.ddvahid.com Copyright © 2007 Frank Vahid Instructors of courses requiring linked's Digital Design textbook (published by John Wiley and Sons) have permission to modify and use these slides for customary course-related activities, subject in keeping the copyright series to place and unmodified. These slides may be posted on a maniform of courses requiring linked's Digital Design textbook (published by John Wiley and Sons) have permission to modify and use these slides for customary course-related activities, subject in keeping the copyright series to be induced and the subject of the subject of

# RTL Design

Behavioral-Level Design: Start with C (or Similar Language)

- Replace first step of RTL design method by two steps

- □ Capture in C, then convert C to high-level state machine

- □ How convert from C to high-level state machine?

Step 1A: Capture in C

Step 1B: Convert to high-level state machine

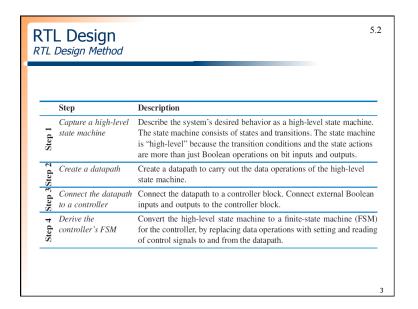

|         | Step                                  | Description                                                                                                                                                                                                                                                                            |

|---------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step 1  | Capture a high-level<br>state machine | Describe the system's desired behavior as a high-level state machine. The state machine consists of states and transitions. The state machine is "high-level" because the transition-conditions and the state actions are more than just Boolean operations on bit inputs and outputs. |

| 3Step 2 | Create a datapath                     | Create a datapath to carry out the data operations of the high-level state machine.                                                                                                                                                                                                    |

| Step 3  | Connect the datapath to a controller  | Connect the datapath to a controller block. Connect external Boolean inputs and outputs to the controller block.                                                                                                                                                                       |

| Step 4  | Derive the controller's FSM           | Convert the high-level state machine to a finite-state machine (FSM) for the controller, by replacing data operations with setting and reading of control signals to and from the datapath.                                                                                            |

RTL Design Converting from C to High-Level State Machine Convert each C construct to equivalent states and transitions Assignment statement Becomes one state with expression assignment o *If-then* statement □ Becomes state with condition check, transitioning to "then" if (cond) { statements if condition true, // then stmts otherwise to ending state o "then" statements would also be converted to states

# RTL Design

Converting from C to High-Level State Machine

- If-then-else

- Becomes state with condition check, transitioning to "then" statements if condition true, or to "else" statements if condition false

- While loop statement

- Becomes state with condition check, transitioning to while loop's statements if true, then transitioning back to condition check

RTL Design Simple Example of Converting from C to High-Level State Machine Inputs: uint X, Y !(X>Y) !(X>Y) Outputs: uint Max ▼ X>Y if (X > Y) { Max = X;Max=X else { Max = Y;(end) o Simple example: Computing the maximum of two numbers Convert if-then-else statement to states (b) ☐ Then convert assignment statements to states (c)

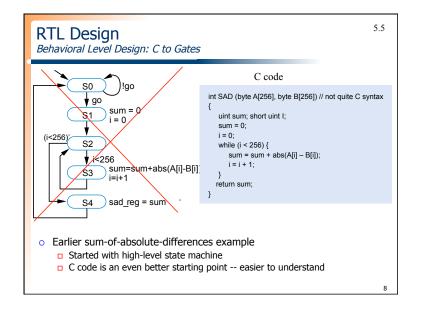

# RTL Design Example: Sum-of-Absolute-Differences C Inputs: byte A[256, B[256] bit go; Output: int sad main() Convert each construct to states Simplify when possible, e.g., merge states uint sum; short uint I; while (1) { while (!go); From high-level state machine, follow RTL design method to create circuit sum = 0; i = 0; while (i < 256) { sum = sum + abs(A[i] - B[i]); i = i + 1; Thus, can convert C to gates using straightforward automatable process } sad = sum; Not all C constructs can be efficiently converted Use C subset if intended for circuit Can use languages other than C, of course 13