```

Top-Down Design - Combinational Behavior to

Structure

Procedures with If-Else Statements

Process may use if-else statements

(a.k.a. conditional statements)

`timescale 1 ns/1 ns

□ if (expression)

module BeltWarn(K, P, S, W);

If expression is true (evaluates to

nonzero value), execute

input K. P. S.

corresponding statement(s)

output W;

reg W;

o If false (evaluates to 0), execute

else's statement (else part is

always @(K, P, S) begin

if ((K & P & ~S) == 1)

optional)

Example shows use of operator ==

else

W <= 0:

→ logical equality, returns true/false

(actually, returns 1 or 0)

endmodule

o True is nonzero value, false is zero

vldd_ch2_BeltWarnBehIf.v

```

```

Top-Down Design - Combinational Behavior to

Structure

Procedures with If-Else Statements

timescale 1 ns/1 ns

module Dcd2x4(I1, I0, D3, D2, D1, D0);

Q: Create procedure describing

input I1, I0;

behavior of a 2x4 decoder using if-else-

output D3, D2, D1, D0;

reg D3, D2, D1, D0;

if construct

always @(I1, I0)

-10 D1-

begin

if (I1==0 && I0==0)

- I1 D2 -

D3 <= 0; D2 <= 0;

D1 <= 0; D0 <= 1;

D3 -

2x4 decoder

else if (I1==0 && I0==1)

Order of assignment statements does

begin

D3 <= 0; D2 <= 0;

not matter.

D1 <= 1; D0 <= 0;

Placing two statements on one line

else if (I1==1 && I0==0)

does not matter.

begin

D3 <= 0; D2 <= 1;

D1 <= 0; D0 <= 0;

To execute multiple statements if

- end

expression is true, enclose them

else

begin

between "begin" and "end"

D3 <= 1; D2 <= 0;

D1 <= 0; D0 <= 0;

end

vldd_ch2_Dcd2x4Beh.v

end

endmodule

```

F V1 Discuss how last else could have been "else if (I1==1 && I0==1)" ? F V, 2/22/2007

```

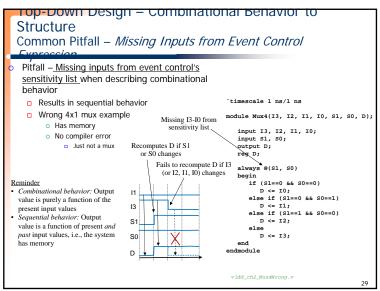

10p-Down Design - Combinational Benavior to

Structure

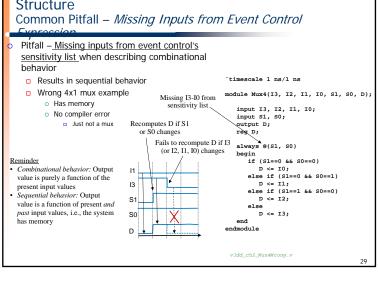

Common Pitfall – Missing Inputs from Event Control

Verilog provides mechanism to help avoid

this pitfall

■ @* – implicit event control expression

`timescale 1 ns/1 ns

Automatically adds all nets and variables

that are read by the controlled statement or module Mux4(I3, I2, I1, I0, S1, S0, D);

statement group

input I3, I2, I1, I0;

o Thus, @* in example is equivalent to

input S1, S0;

@($1,$0,10,11,12,13)

output D:

reg D;

o @(*) also equivalent

always @*

begin

if (S1==0 && S0==0)

D <= I0;

else if (S1==0 && S0==1)

D <= I1:

else if (S1==1 && S0==0)

D <= I2;

else

D <= I3:

```

```

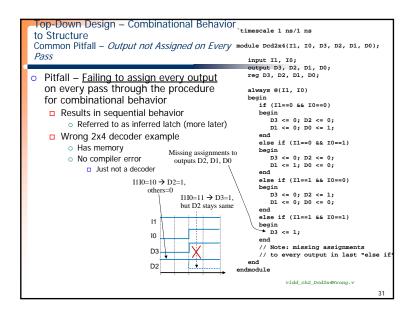

Top-Down Design – Combinational Behavior to

Structure

Common Pitfall – Output not Assigned on Every Pass

Same pitfall often occurs due to not considering all

possible input combinations

if (I1==0 && I0==0)

begin

D3 <= 0; D2 <= 0;

D1 <= 0; D0 <= 1;

else if (I1==0 && I0==1)

D3 <= 0: D2 <= 0:

D1 <= 1; D0 <= 0;

else if (I1==1 && I0==0)

begin

D3 <= 0; D2 <= 1;

Last "else" missing, so not all

D1 <= 0; D0 <= 0;

input combinations are covered

(i.e., I1I0=11 not covered)

```

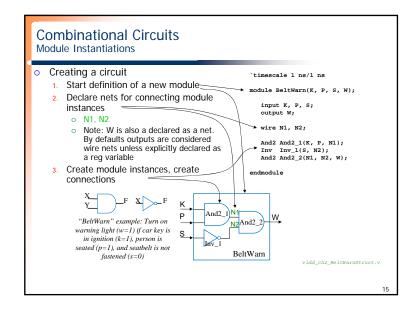

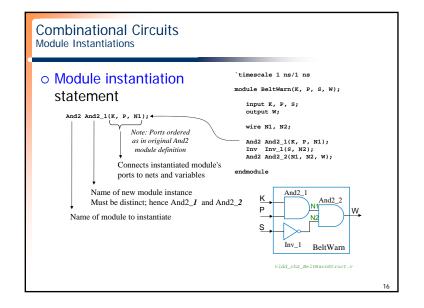

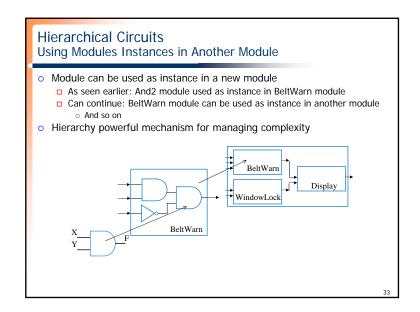

## **Built-In Gates** We previously defined AND, OR, and NOT gates Verilog has several built-in gates that can be instantiated and, or, nand, nor, xor, xor `timescale 1 ns/1 ns One output, one or more inputs o The output is always the first in the list module BeltWarn(K, P, S, W); of port connections input K, P, S; Example of 4-input AND: and a1 (out, in1, in2, in3, in4); wire N1, N2; not is another built-in gate and And\_1(N1, K, P); not Inv\_1(N2, S); and And\_2(W, N1, N2); Earlier BeltWarn example using built-in gates Note that gate size is automatically determined by the port connection list vldd\_ch2\_BeltWarnGates.v