## ECE 274 Digital Logic - Fall 2008

## Sequential Logic Design – Sequential Logic Design Process

Digital Design 3.4 – 3.5

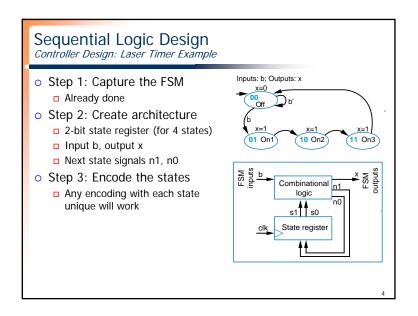

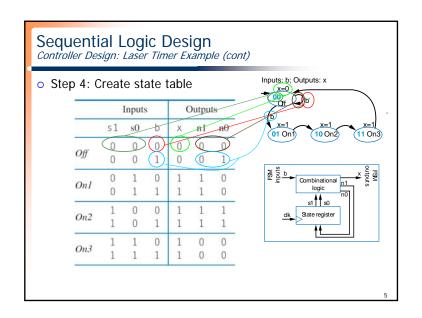

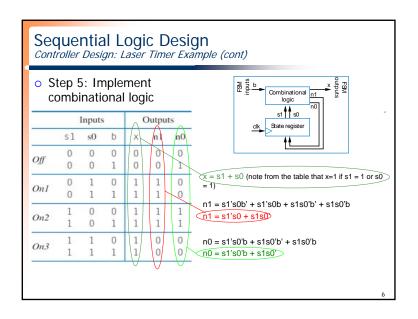

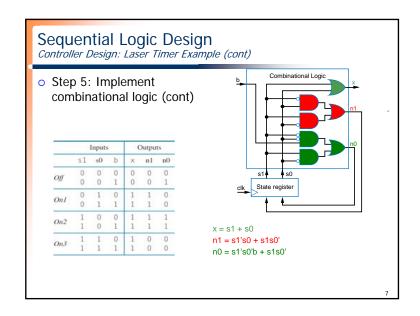

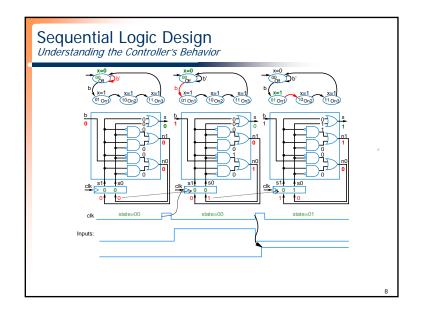

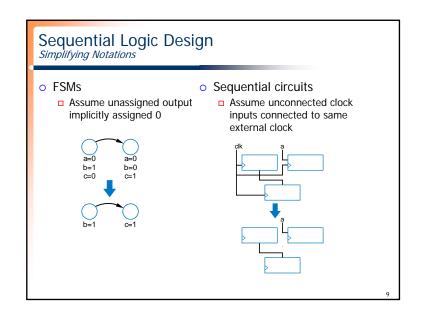

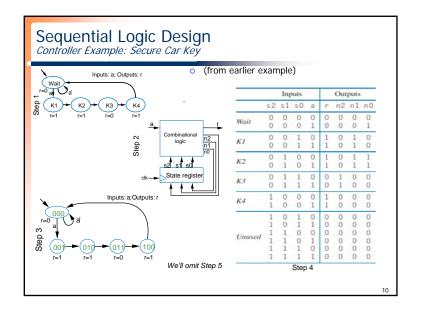

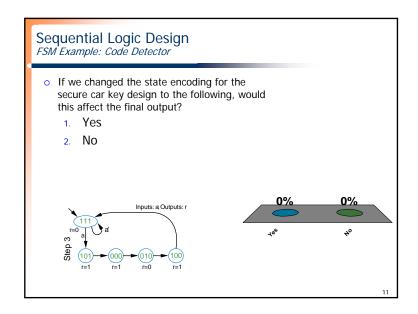

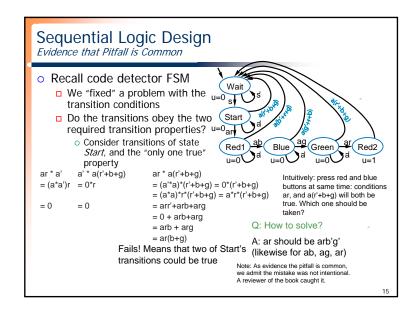

## Sequential Logic Design Controller Design Five step controller design process Capture the FSM Create an FSM that describes the desired behavior of the controller. Create the Create the standard architecture by using a state register of architecture appropriate width, and combinational logic with inputs being the state register bits and the FSM inputs and outputs being the next state bits Assign a unique binary number to each state. Each binary number representing a state is known as an encoding. Any encoding will do as long as each state has a unique encoding. Create a truth table for the combinational logic such that the logic Create the state table will generate the correct FSM outputs and next state signals. Ordering the inputs with state bits first makes this truth table describe the state behavior, so the table is a state table. Implement the Implement the combinational logic using any method. combinational logic

## Sequential Logic Design More on Flip-Flops and Controllers

- Other flip-flop types

- □ SR flip-flop: like SR latch, but edge triggered

- □ JK flip-flop: like SR  $(S \rightarrow J, R \rightarrow K)$

- But when JK=11, toggles

- o 1→0, 0→1

- □ T flip-flop: JK with inputs tied together

- o Toggles on every rising clock edge

- □ Previously utilized to minimize logic outside flip-flop

- o Today, minimizing logic to such extent is not as important

- o D flip-flops are thus by far the most common

3.5