.: Core Research Activities in

Reconfigurable Computing Laboratory

|

Domain-Focused Advanced Software-Reconfigurable Heterogeneous System on Chip (DASH-SoC)

Please refer to Compiler-Integrated Emulation Environment and DSSoC Runtime (CEDR) project page for current state of the project.

Funded by: DARPA

Collaborators: Arizona State University, University of Michigan, Carnegie Mellon

Students: Nirmal Kumbhare, Joshua Mack, Sahil Hassan

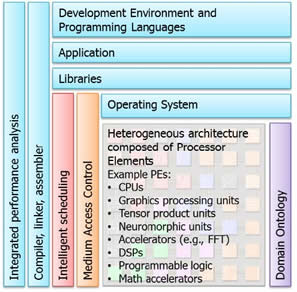

The DASH-SoC team solves critical challenges, which include identifying the appropriate SoC capabilities and simplifying system implementations. We develop intelligent design-time and real-time tools to improve SoC throughput, latency, power efficiency, and flexibility. We promote the use and development of open tools to enable broader applicability. We develop intelligent algorithms that identify the underlying ontologies of a set of important applications that include communications, radars, and SIGINT, and translate this information to specific application-domain SoC architectures, including processing element (PE) specification. We dramatically extend current compiler and debugging tools to address the needs of heterogeneous SoCs. We develop an innovative dynamic intelligent scheduler (IS), which learns from observing needs and performance metrics, to remove the requirement for domain-expert tuning of threading. In tight coordination with the IS and software tools, we design sophisticated on-chip media-access-control (MAC) capabilities that enable on-chip communications to the PEs.

|