## Module 1: Introduction to ADE 5.0

#### **Topics in this module**

- Course objectives

- Course outline

- Class schedule

- Getting help, technical support, and documentation

- The Design Framework II Design Environment

- Accessing design tools

- Creating a library

- Creating cells and cell views

- Schematic capture

- Analog simulation

- Analyses

- Summary

### **Terms and Definitions**

| CDSDoc         | Cadence <sup>®</sup> online help tool that uses a Netscape browser interface. |

|----------------|-------------------------------------------------------------------------------|

| CIW            | Command interpreter window. Interface used to access DFII applications.       |

| command line   | A line buffer in the CIW that accepts SKILL-based commands.                   |

| text field     | An area on a tool window where the user provides data.                        |

| cyclic field   | Set of selectable options in a tool window, denoted by a small rectangle.     |

| library        | A set of design directories that includes 'cells' and 'cellviews'.            |

| Library Manage | A Cadence tool that allows user to browse and edit a design library.          |

| Composer       | Schematic editor and symbol generation tool in DFII.                          |

| cell           | A basic unit of a design hierarchy described by cell views.                   |

| cell view      | A specific view of a cell that includes schematic, symbol, or layout.         |

| instance       | A uniquely named placement of a symbol onto a schematic.                      |

| pin            | A connection point on a schematic and symbol used for accessing signals.      |

| bindkey        | A predefined key on the keyboard that invokes a preselected command.          |

## **Course Objectives**

- Learn how to create schematics, symbols, and a design hierarchy

- Set up and run analog simulations

- Analyze simulation results

- Evaluate sensitivities and mismatches to improve circuit performance.

- Run Corners, Monte Carlo, and Optimization tools to improve yield

- Create and use OCEAN scripts and SKILL to set up and run simulations

- Understand the Component Description Format (CDF)

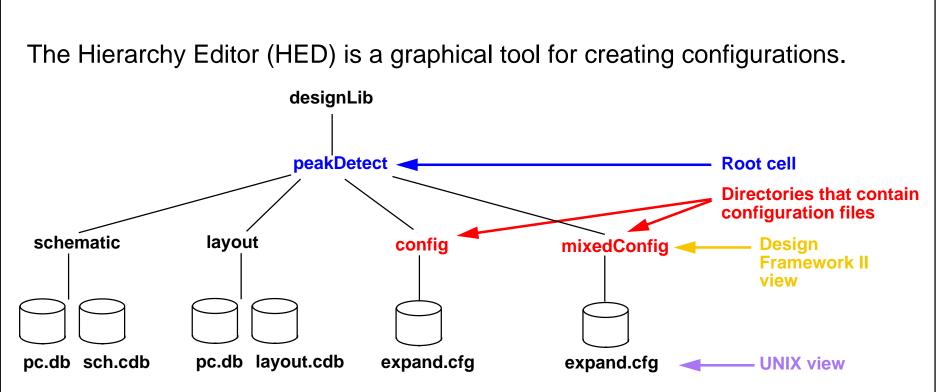

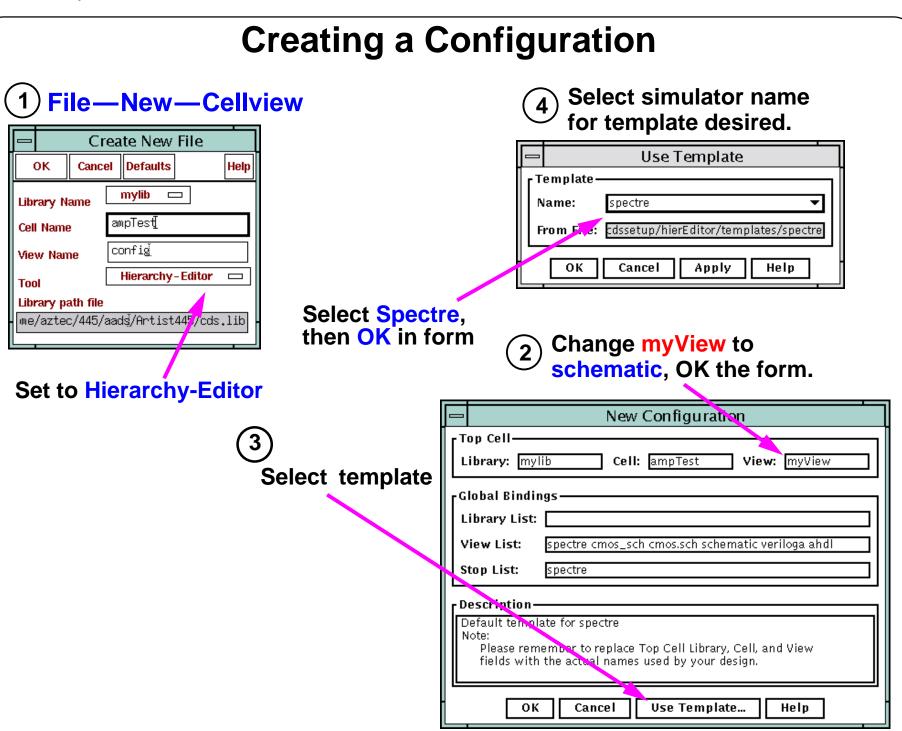

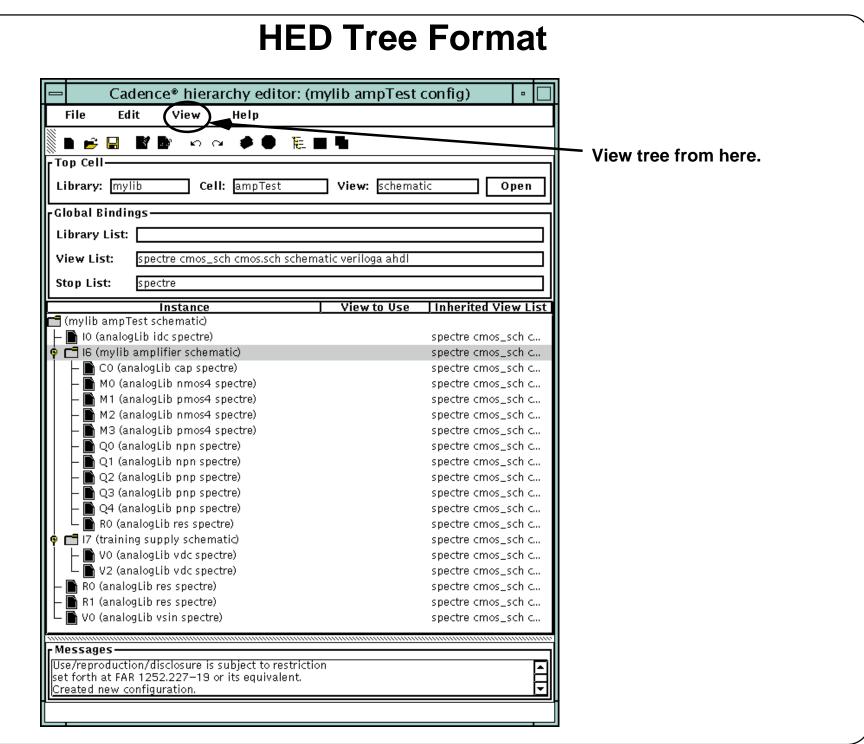

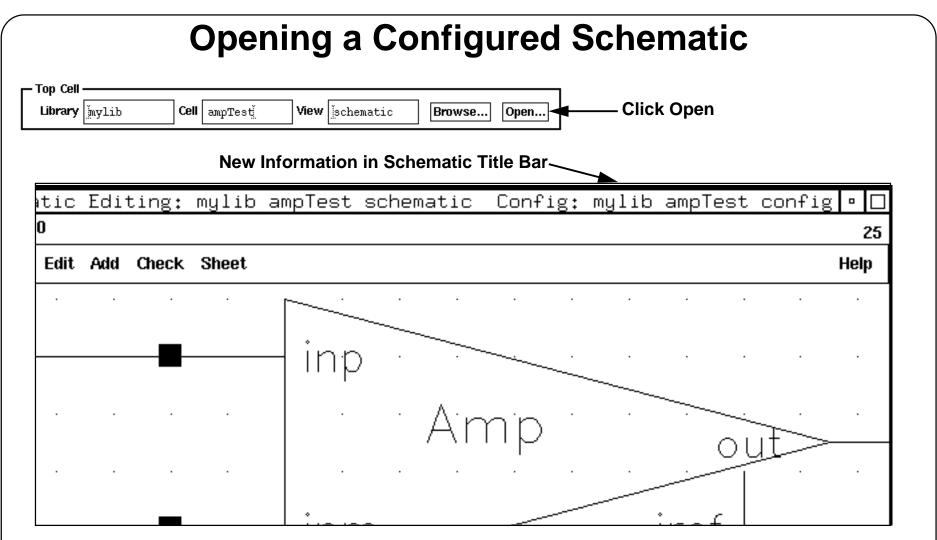

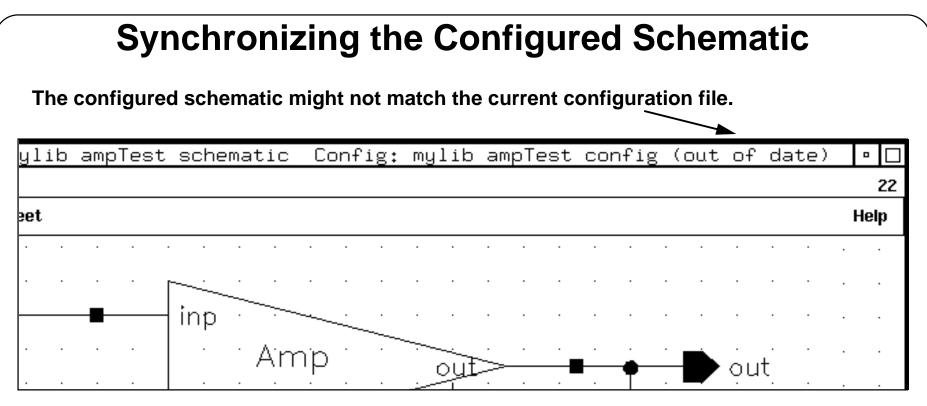

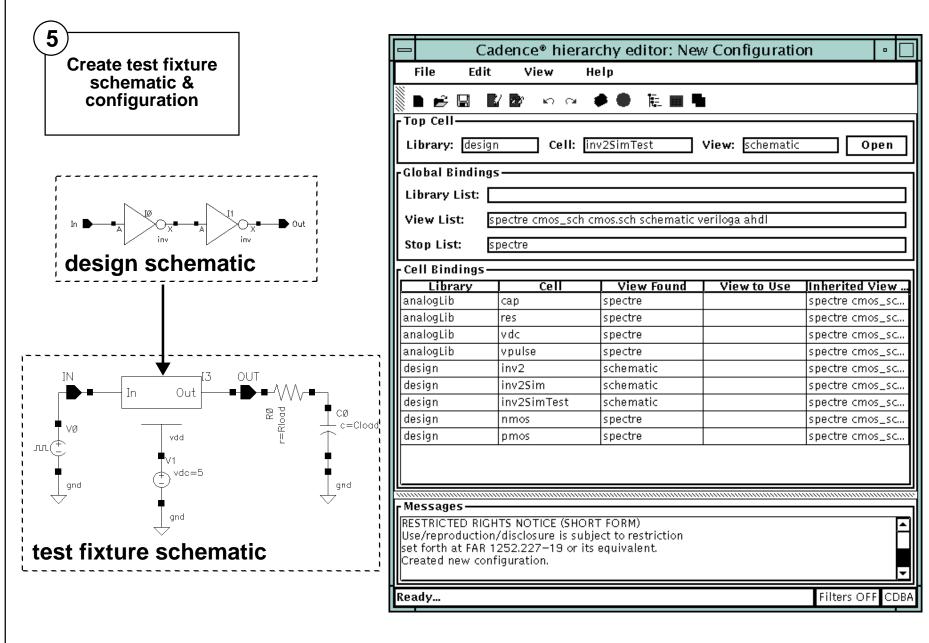

- Create configurations with the Hierarchy Editor (HED)

- Use subcircuits and macromodels

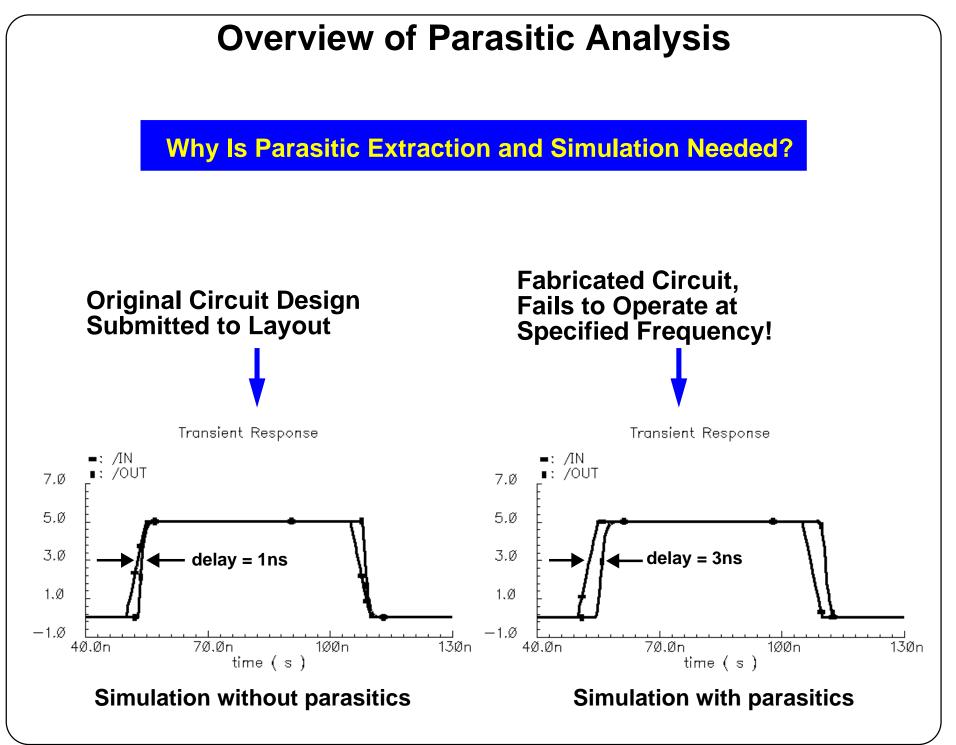

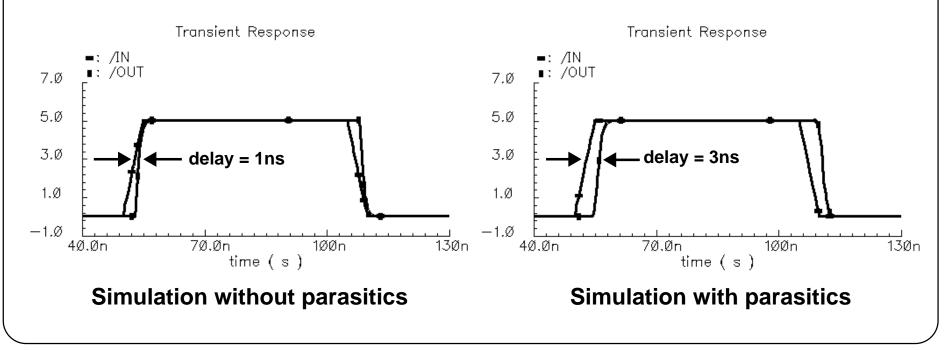

- Run the parasitic simulation flow

- Use advanced tools to solve special problems

## **Course Objectives**

The objective of this class is to provide both instruction and materials on using the Cadence Analog Design Environment. The objective for this course of instruction is that the student can utilize the entire front-to-back design flow of the Analog Design Environment software.

# **Course Outline**

- 1 Introduction to ADE 5.0

- 2 Schematic Entry

- 3 Analog Simulation

- 4 Simulation Results Display Tools

- 5 Analyzing Simulation Results

- 6 SKILL and OCEAN

- 7 Parametric Analysis

- 8 Corners Analysis

- 9 Monte Carlo Analysis

- 10 Optimization Analysis

- 11 Circuit Surfer

- 11 Component Description Format (CDF)

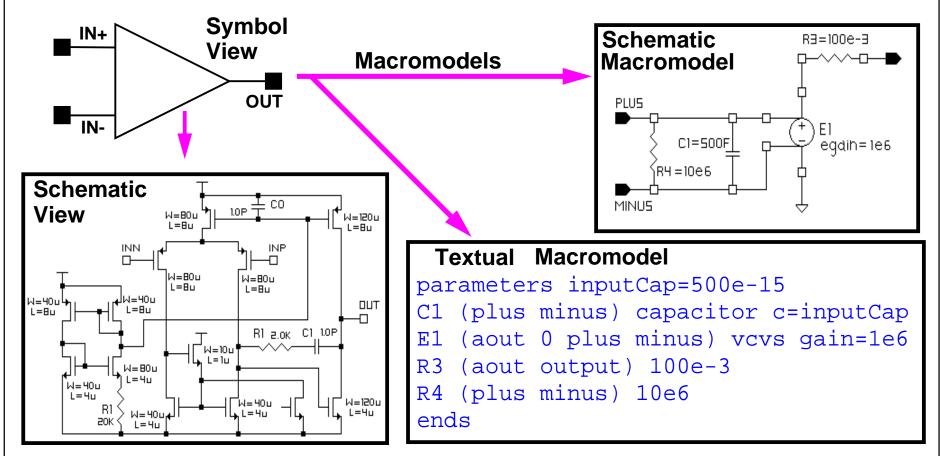

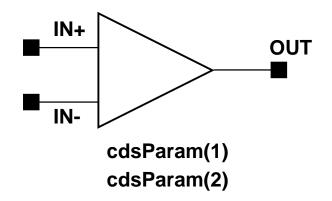

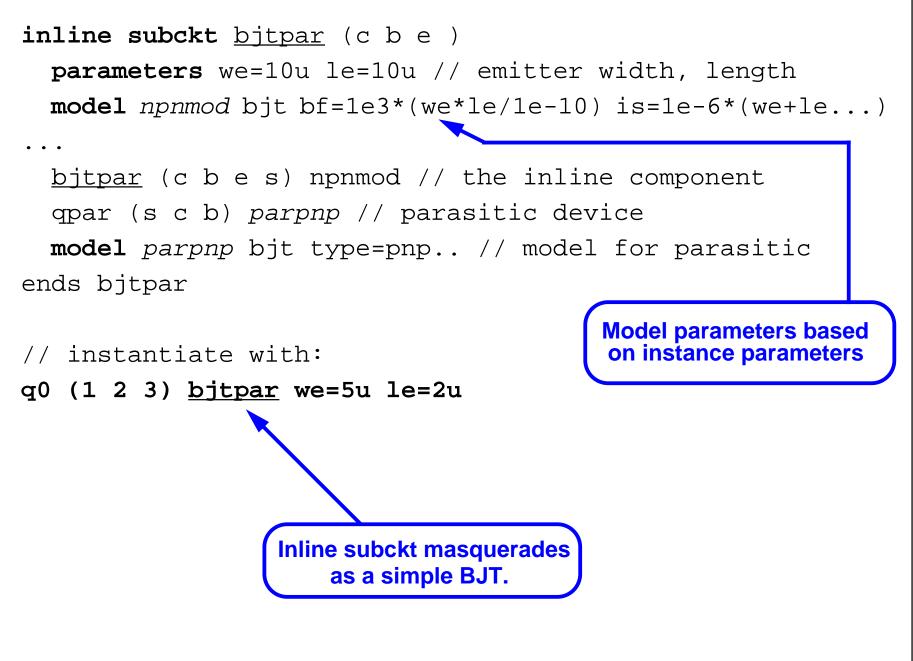

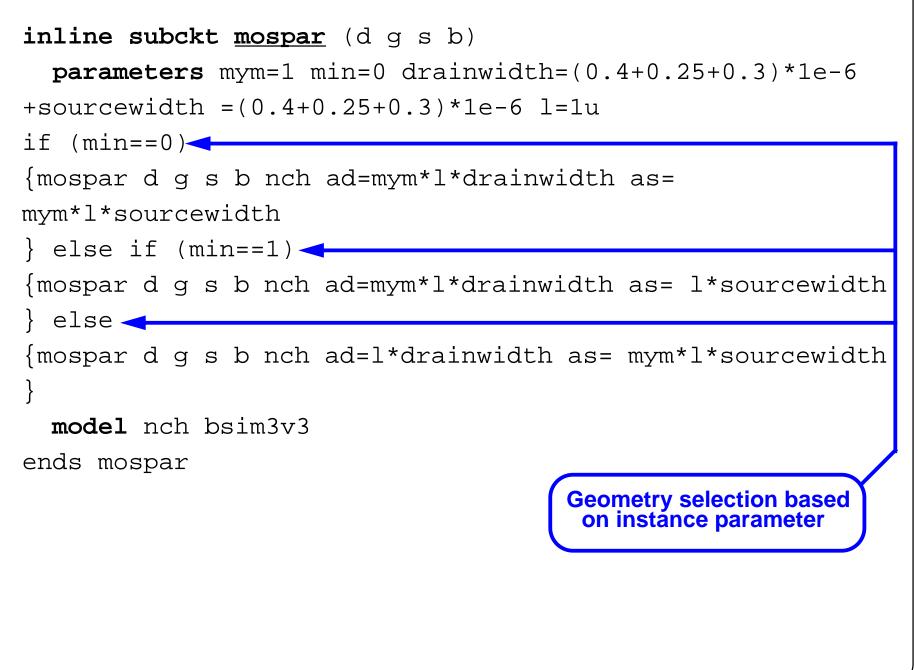

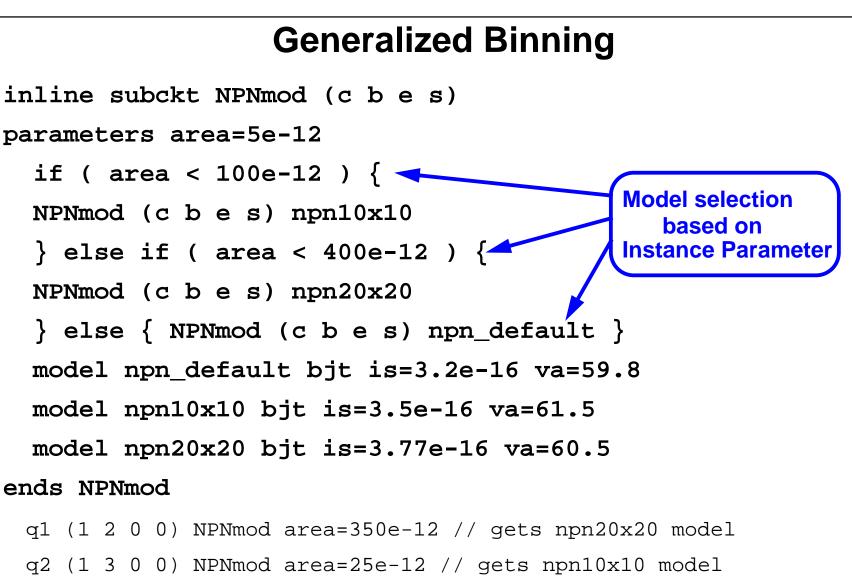

- 12 Macromodels, Subcircuits, and Inline Subcircuits

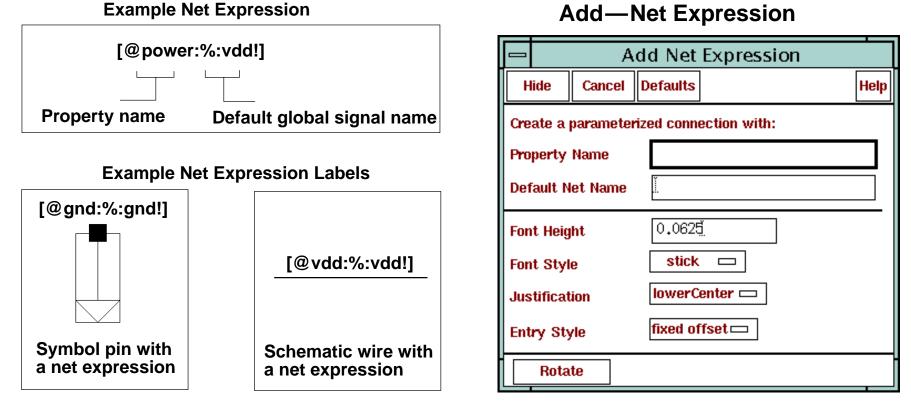

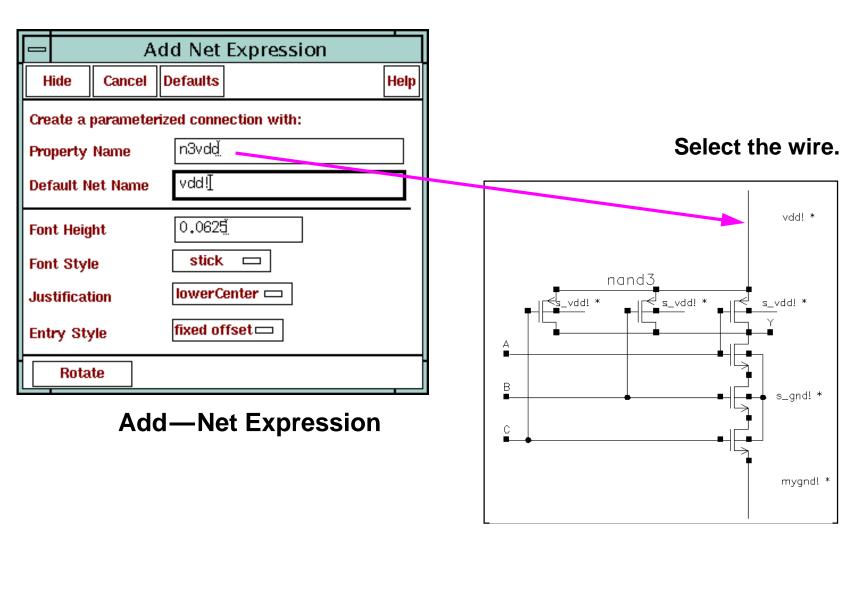

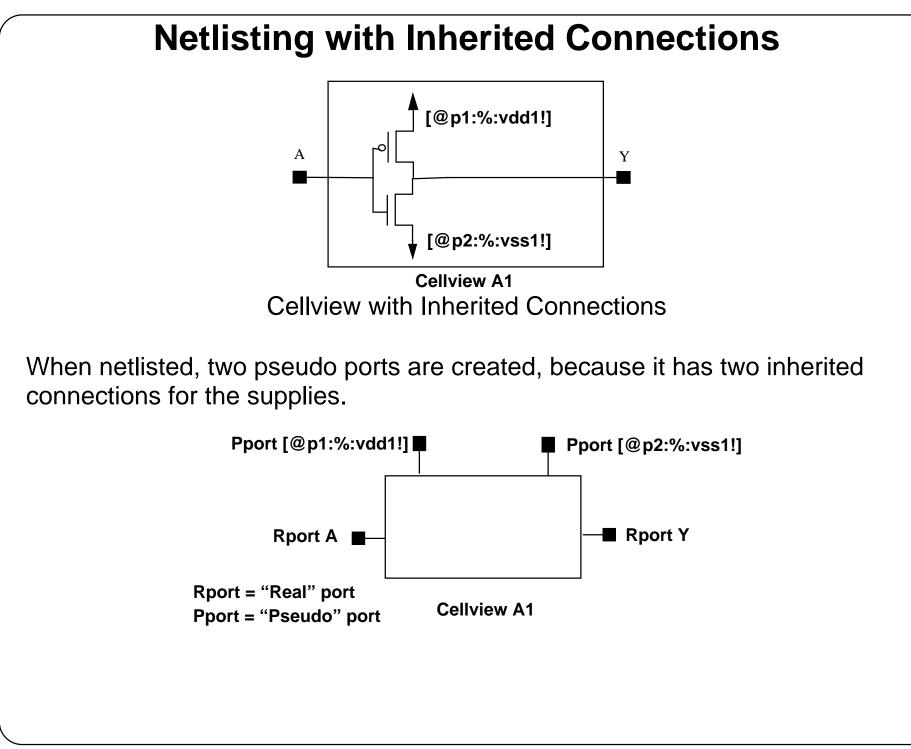

- 13 Inherited Connections

- 14 The Hierarchy Editor

- 15 Overview of Parasitic Simulation

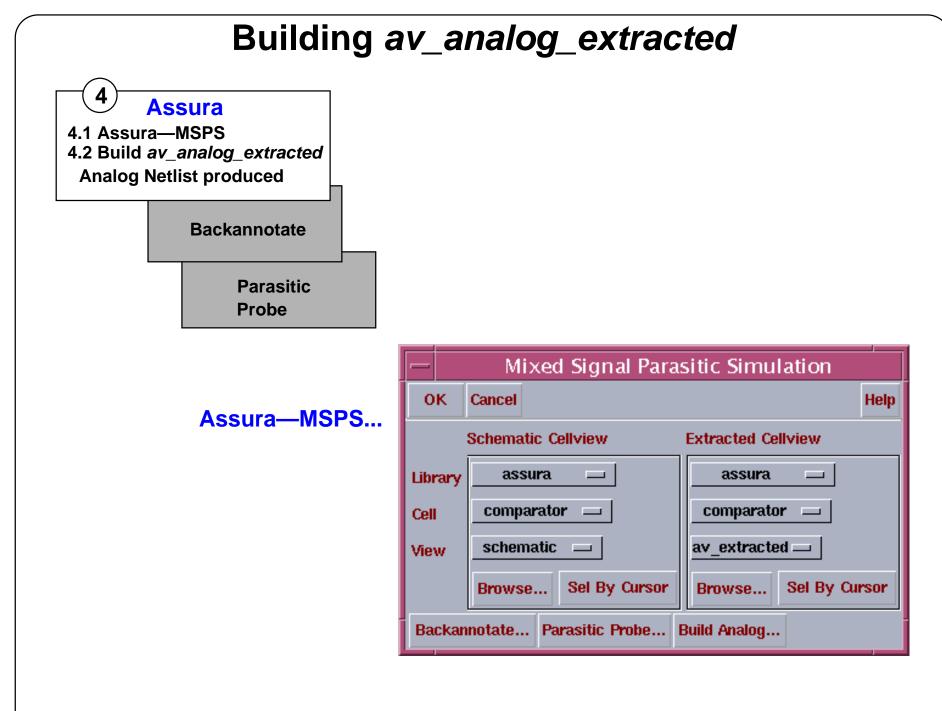

- 16 Assura Parasitic Simulation Flow

#### Appendixes:

- A Diva Parasitic Simulation Flow

- B WaveScan Display Tools

- C Spectre MDL

- D Match Analysis, dcmatch

- E Advanced Topics in ADE

### **Course Outline**

The Analog Design Environment classroom series is an intensive, fast-paced, 4-day class on using Cadence design software to run analog circuit simulations.

This Analog Design Environment course comprises 17 modules, including both lectures and corresponding lab activities.

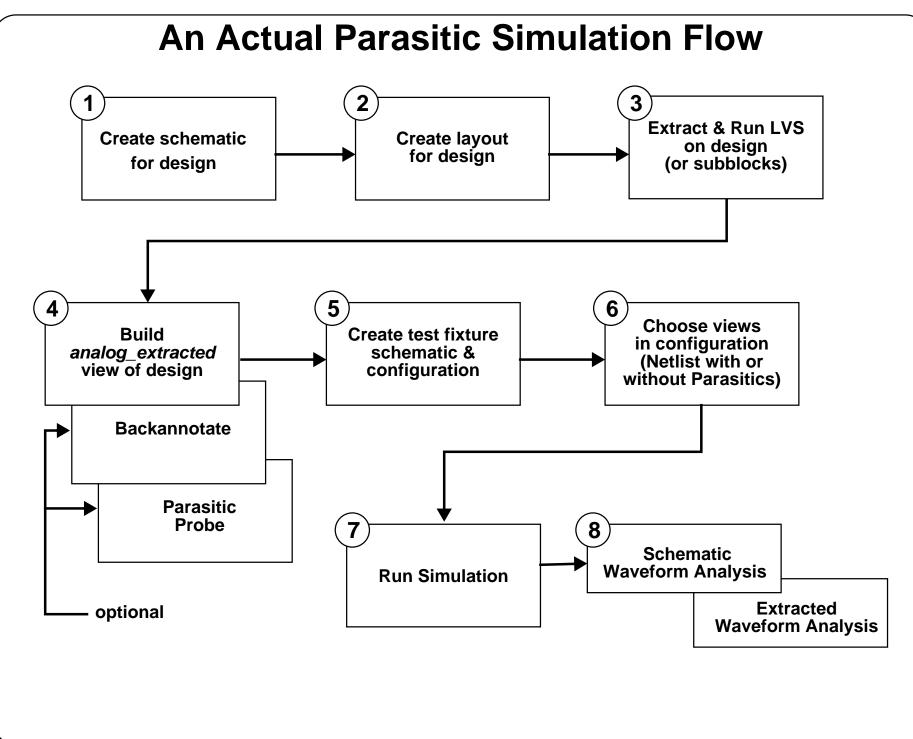

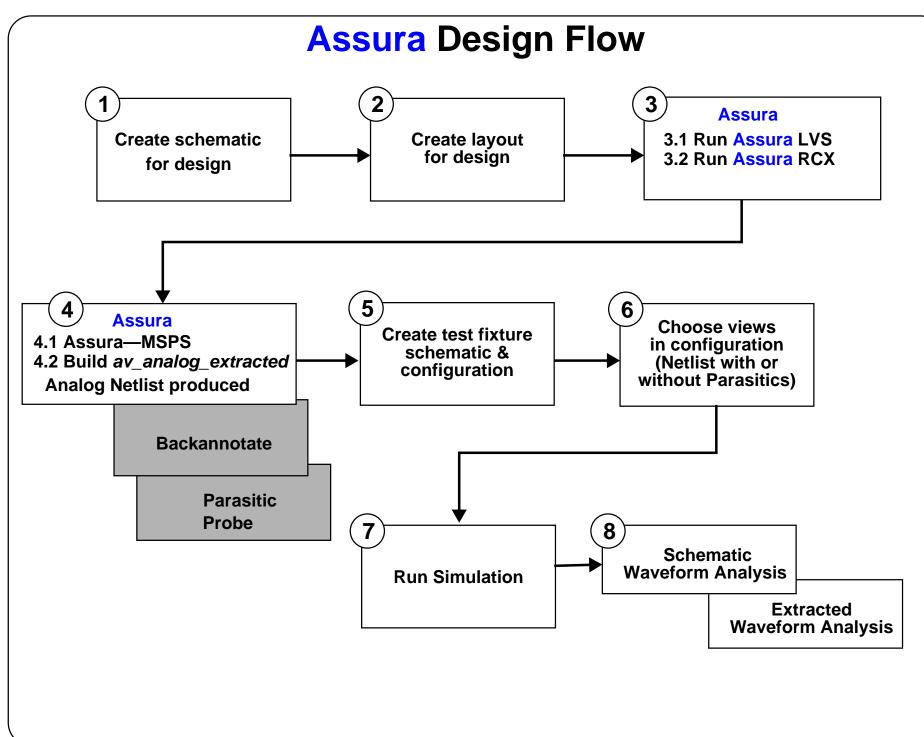

Module 15 provides an overview of the Parasitic Simulation theory and flow, followed by Module 16, Assura Parasitic Simulation Flow. Appendix A, Diva Parasitic Simulation Flow, will be taught when conditions require this flow to be used. The selection of Diva or Assura will be based on the specific classroom and work site circumstances.

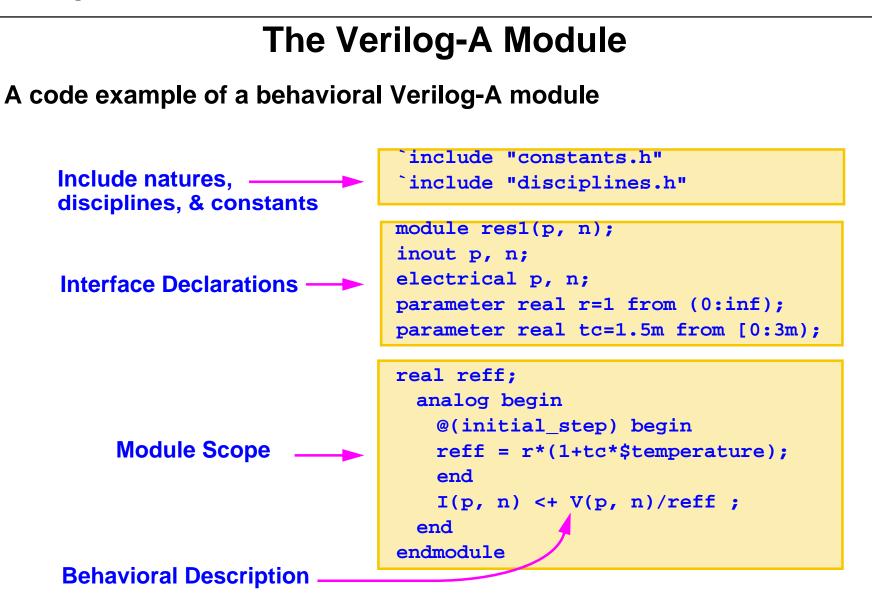

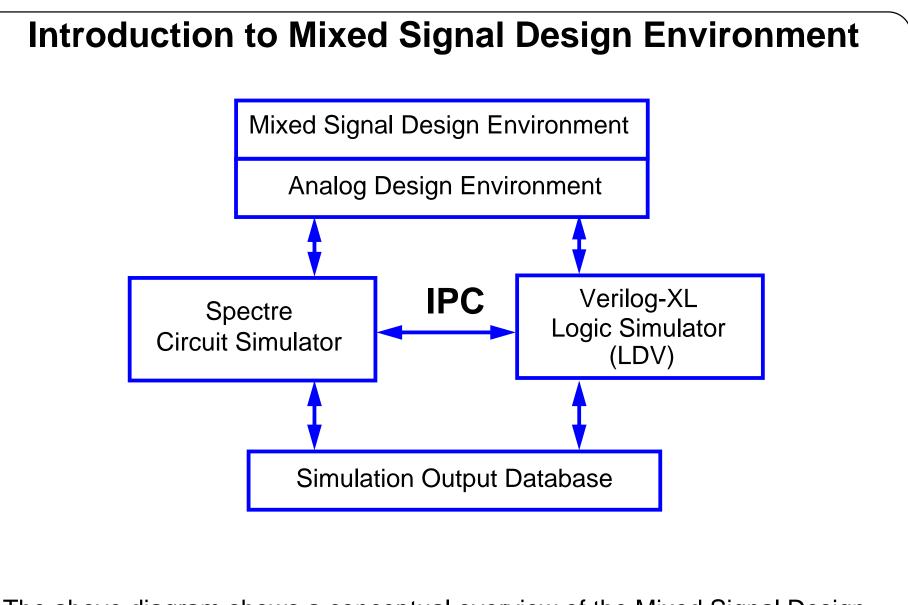

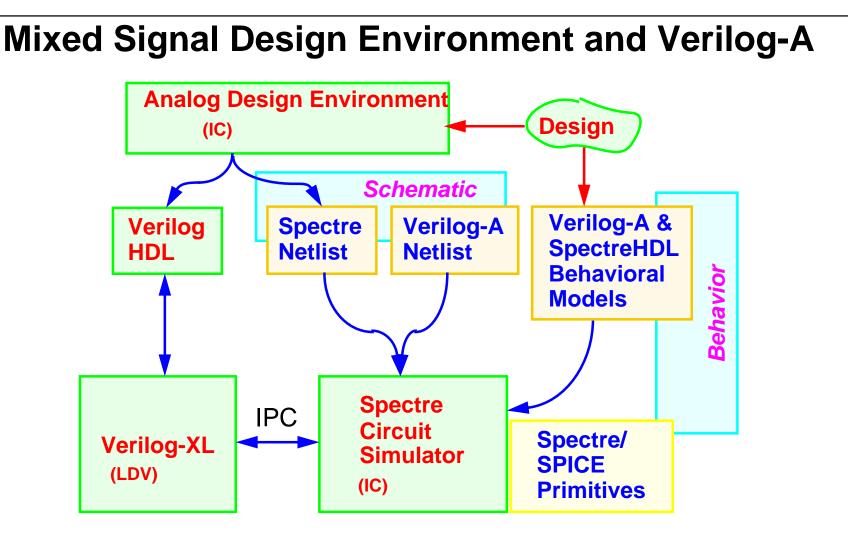

The Appendixes B, C, and D discuss other tools and features of the Analog Design Environment. Finally, Appendix E, Advanced Topics in ADE, provides a brief overview of Verilog-A and Mixed Signal Design Environment.

## **Class Schedule**

#### Day 1

- 1 Introduction to ADE 5.0

- 2 Schematic Entry

- 3 Analog Simulation

- 4 Simulation Results Display Tools

#### Day 2

- 5 Analyzing Simulation Results

- 6 SKILL and OCEAN

- 7 Parametric Analysis

- 8 Corners Analysis

- 9 Monte Carlo Analysis

#### Day 3

- 10 Optimization Analysis

- 11 Circuit Surfer

- 11 Component Description Format (CDF)

- 12 Macromodels, Subcircuits, and Inline Subcircuits

#### Day 4

- 13 Inherited Connections

- 14 The Hierarchy Editor

- 15 Overview of Parasitic Simulation

- 16 Assura Parasitic Simulation Flow

- **Class Evaluations**

### **Class Schedule**

The class schedule listed above is the recommended schedule for the standard 4-day classroom series of ADE 5.0. Private classes taught at customer facilities may require adjustments or modifications to this schedule.

The class schedule is intended to adequately cover all topics of the ADE course. As such, each day covers 4 to 5 modules. Each module requires 1 to 2 hours to complete both the lecture presentation and the lab activity.

To ensure adequate coverage of the lecture material, the instructor may elect to defer answers to detailed questions that are asked during the lecture. The instructor may also deviate from course schedule due to conditions that cause unexpected delays or other circumstances. In any case, the instructor will attempt to answer relative questions in a timely manner or obtain the answer for the student as soon as possible.

# **Getting Help**

You can get help with Cadence software from the following sources:

- Help button on forms and windows

- Cadence online documentation (CDSDoc)

- Education Services training manuals

- SourceLink® online customer support

- Customer Response Center (CRC)

## **Getting Help**

### **Online Help**

Cadence reference manuals and online help files for each product are installed automatically when installing the product. Hard copies of the reference manuals are available from Cadence. All these online documents are part of the online help system, which can be accessed as follows:

- View relevant product information by clicking the help button on windows and forms.

Use this information to complete a form or what can be done in the window.

- Start the CDSDoc documentation from a UNIX shell by typing cdsdoc& at the command line and search through all Cadence reference manuals and online help systems installed with each product. Also, use CDSDoc to print the reference manuals entirely or just the relevant material.

### **Other Means of Getting Information**

- With a software maintenance agreement, subscribe to the SourceLink online support system and view known problems and solutions or communicate with other users. The SourceLink system is accessible via the internet. To open an account, send email to crc\_customers@cadence.com.

- Training manuals, like this one, can supplement reference manuals.

- When the above information is insufficient, call the Customer Response Center.

## **Overview of Analog Design Environment**

Analog Design Environment is a software tool set within Design Framework II that is used to set up and run analog simulations. The Analog Design Environment also accesses and views the simulation results.

The Analog Design Environment allows you to:

- Choose the simulator host

- Choose the type of analysis: ac, dc, transient, parametric, sensitivity, etc.

- Set design variables: Vdd, frequency, Cout, etc.

- Append model files and include files

- Netlist and run simulations

- Quickly alter the simulation setup and rerun the simulation

- Plot simulation results in the Waveform display tool

- Evaluate simulation results using waveform expressions

- Run multiple simulation tools: Corners, Monte Carlo, Optimizer, etc.

- Automatically set up, save, and run OCEAN scripts

### **Overview of Analog Design Environment**

The Analog Design Environment is a set of software design tools used to set up, control, and run circuit simulations. ADE allows you to choose the simulator host, set design variables, select model files, and to select analyses to add, modify, or delete from next simulation run.

The Analog Design Environment provides a user-friendly graphical interface that includes pull-down menus and icons for making fast and easy changes.

The Analog Design Environment also provides control for accessing the simulation results and displaying the results to the Waveform Display tool. The results can be entered into other tools for waveform processing or to obtain specific data using expressions.

The Analog Design Environment provides access to multiple simulation tools. ADE can be used to start Corners, Monte Carlo, and the Circuit Optimizer.ADE also allows you to automatically set up, save, and run OCEAN scripts.

Introduction to ADE 5.0

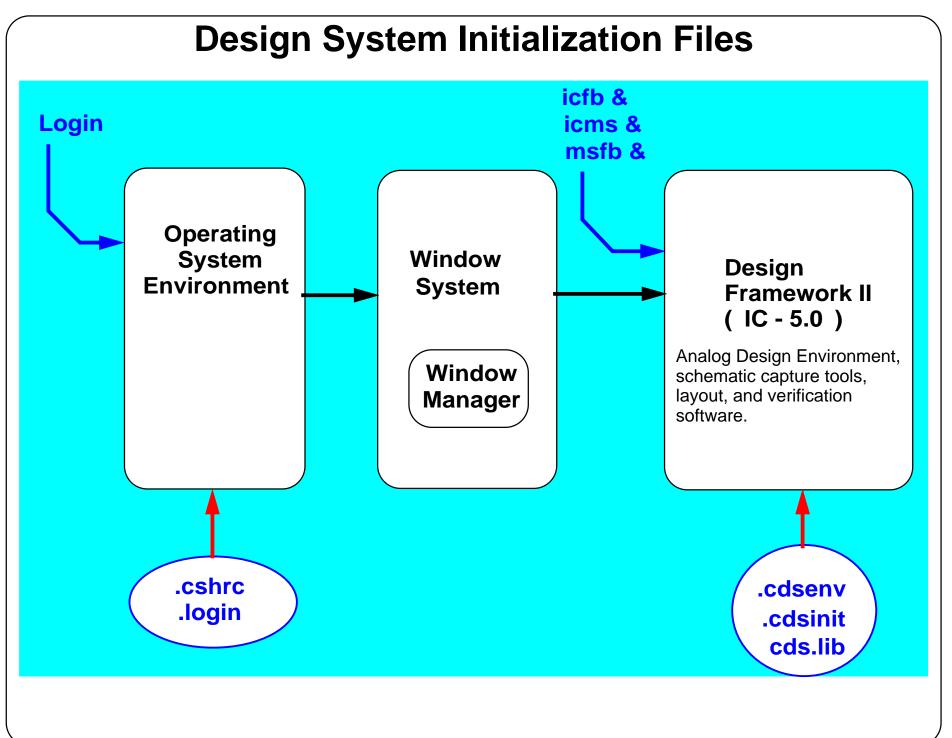

### **Design System Initialization Files**

There are some design system initialization files that configure the operating system environment. For example, the *.cshrc* and *.login* files configure the UNIX environment when you log in and start a UNIX application.

The initialization file, *.cdsinit*, customizes the Analog Design Environment. The *cds.lib* file sets the paths to the libraries. These files, along with the *.cdsenv* file, are discussed later.

For more information on configuring your operating system environment for the Analog Design Environment, consult the *Cadence Design Framework II Configuration Information* guide.

Introduction to ADE 5.0

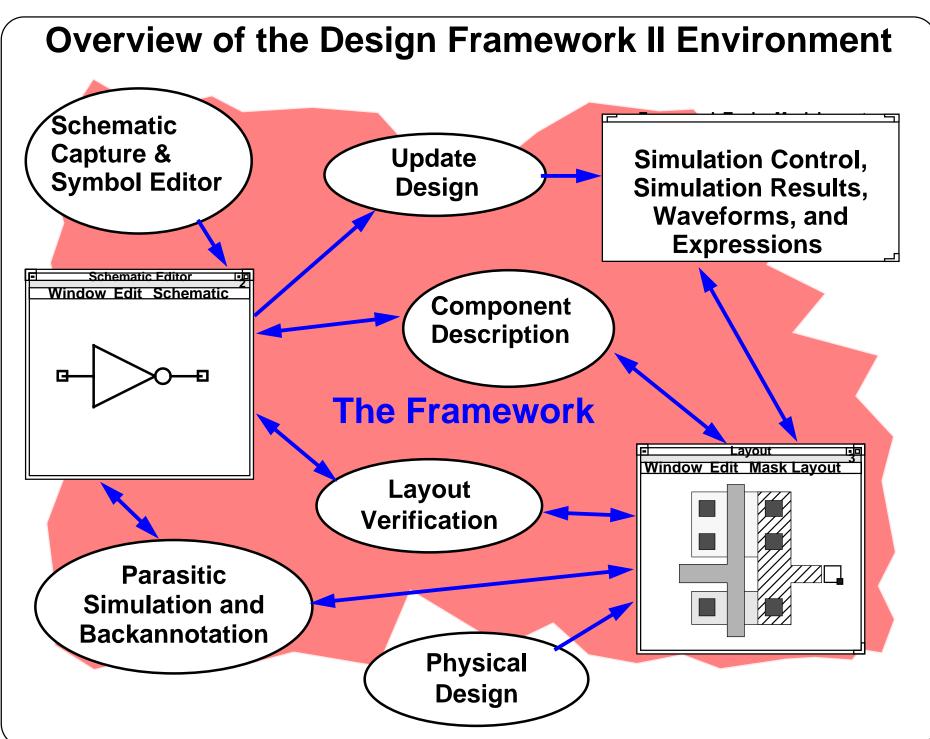

### **Overview of the Design Framework II Environment**

The Cadence Analog Design Environment is a set of design tools that operate within Design Framework II. Design Framework II is the underlying structure for Cadence design tools for schematic capture, analog simulation, and layout. It provides a single integrated environment for accessing all tools and design data, including the ability to:

- Access to the Command Interrupter Window (CIW) using *icfb*, *icms*, or *msfb*.

- Use the Library Manager Tool to browse design libraries and open cell views.

- Create new libraries, cells, and cell views.

- Start or edit a schematic view or symbol view.

- Start or edit a layout design.

- Run layout verification.

- Start the Analog Design Environment and run simulations.

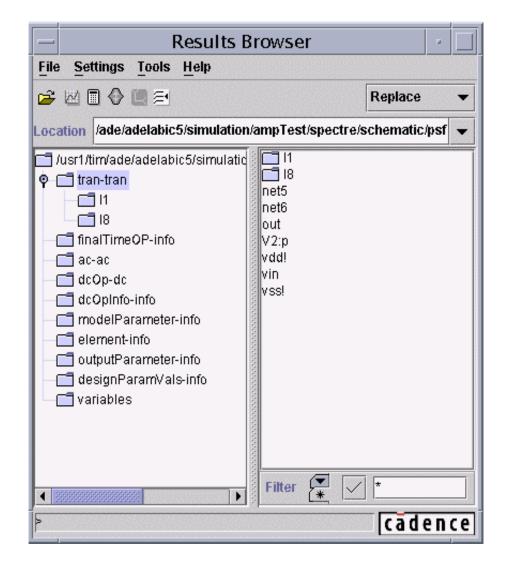

- Access simulation results directly using the Results Browser.

- Run OCEAN scripts.

## Advantages of Using Design Framework II

- Common software environment for using schematic capture, simulation, layout, and design verification

- Easy-to-learn, consistent user interface

- Similar appearance between most forms and windows

- Communication between software tools within the DFII environment

- Tool windows remain open while running other applications

- Data can be "back annotated"

- From layout to schematic

- From simulation to schematic

- From simulation to layout

- etc.

- Applications may be customized or automated using SKILL or the OCEAN command language

### **Advantages of Using Design Framework II**

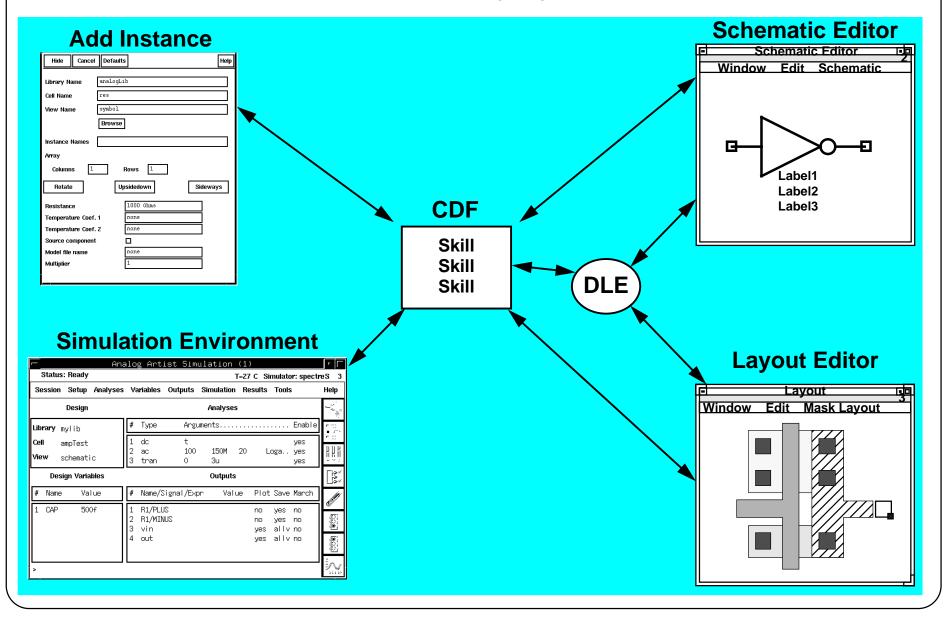

The Cadence Design Framework II environment is an integrated design environment. An integrated environment means that numerous tools and applications operate together. For Design Framework II the environment provides schematic capture, simulation control, netlist generator, circuit simulator, waveform display, layout and verification tools.

For the design software tools, DFII provides:

■ Consistent user interface

Analog applications in the design framework have the same "look and feel." Menu items are often in the same place in every application.

■ Consistent database

A consistent database stores all design information. Tools share data in real time so long formalized translations between tools are not needed. The DFII environment also saves time during schematic to layout verification, because it updates layout geometries as the schematic component parameters change.

#### Cooperating tools

Applications run concurrently, with results available to all other tools, eliminating the need to open and close applications when changing tool contexts. For example, update and simulate a schematic without restarting the simulation environment. Updates are known to the simulation window as soon as they are made in the schematic entry window.

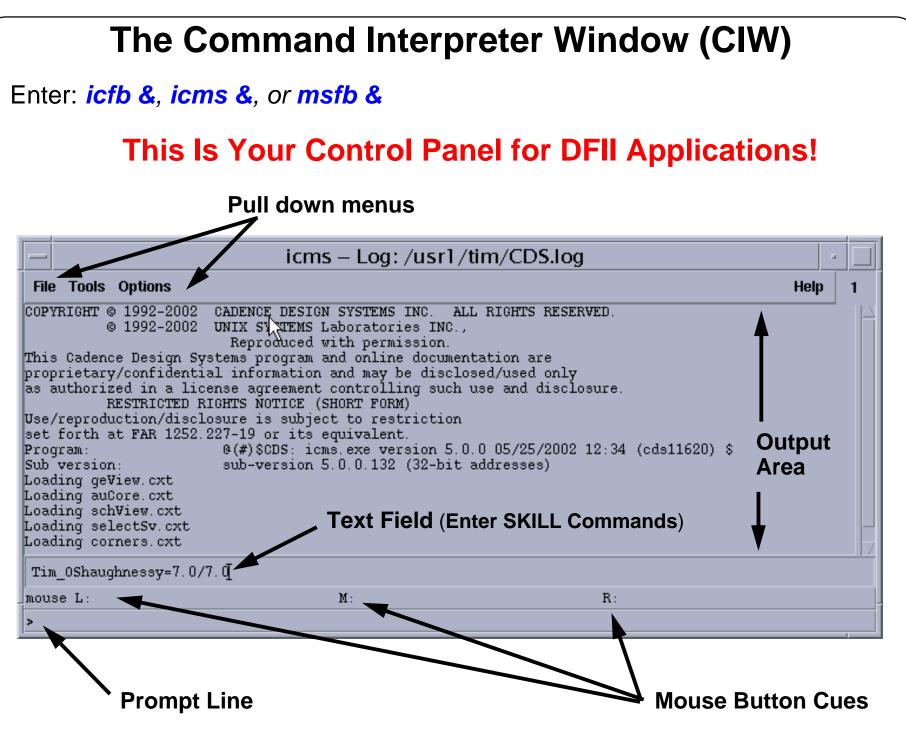

### **The Command Interpreter Window (CIW)**

The Command Interpreter Window (CIW) is at the heart of the framework system. Use this window to access framework-based applications. System and error messages from applications are reported in this window.

#### Output Area

The output area displays a running history of the commands used with their results. For example, it issues a status message when a cell library is opened. This data is saved in the *Log File* whose path appears as the application title of the CIW. Use scroll bars to view previous output pane data without having to resize the CIW.

#### Text Entry Field

Enter Cadence SKILL commands in this area. Every pull-down menu command in the Design Framework II environment has an equivalent SKILL command. Advanced users can define and execute their own SKILL commands by entering them here.

#### Prompt Line

The prompt line at the bottom of the CIW indicates the next step when carrying out a command executed in any Design Framework II application window.

#### Mouse Button Cues

Tells which mouse button to push to execute a command in a Design Framework II window.

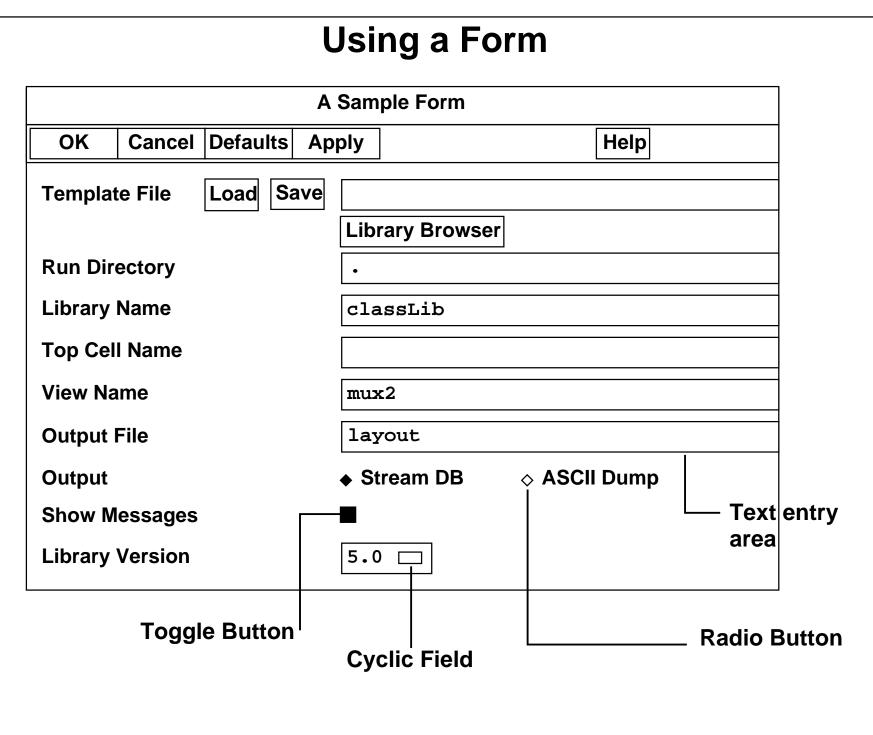

### Using a Form

Forms provide a place to enter the information required by a command.

The top of the form has a *title bar* and a set of *banner buttons*. The body of the form contains *prompts* that indicate which option is being set. Next to the prompt is one of the following:

- *radio button*, for choosing one of several options

- *text entry area*, for typing information

- *toggle button*, for turning options on or off

- *cyclic field*, for choosing one of many options. Initially only one option is shown. Move the pointer to the field and hold down the left mouse button, the other options appear.

The form might also have buttons such as *Browse*, which shows a browser window, or *More Options*, which displays another form.

Change of an entry on a form is disabled when the name appears in gray instead of black, and the text entry area is shaded.

- Press the **Tab** key or mouse to move to the next text entry field.

- Use the left and right arrows on the keyboard to move the cursor in a text entry field.

Press **Control-a** to go to the beginning of a line; **Control-e** to go to the end of a line; **Control-u** to erase to the beginning of a line.

# Initializing the Design Framework II Environment

The Design Framework II software reads your *.cdsinit* file at startup to set up your environment. The *.cdsinit* file:

- Sets user-defined bindkeys when the Design Framework II environment is started.

- Redefines system-wide defaults.

- Contains SKILL commands.

The search order for the .cdsinit file is:

- <install\_dir>/tools/dfll/local

- the current directory

- the home directory

Here is the path to a sample .cdsinit file:

<install\_dir>/tools/dfII/samples/artist/cdsinit

### **Initializing the Design Framework II Environment**

Start the Design Framework II environment, it reads the *.cdsinit* file to set up your configuration. The search order for the *.cdsinit* file is *<install\_dir>/tools/dfII/local*, the current directory, and finally the home directory. When a *.cdsinit* file is found, the search stops unless a command in a *.cdsinit* file reads other user files.

The *.cdsinit* file is a text file written in SKILL. A statement in a *.cdsinit* file can load user-defined bindkeys. Another statement might set Waveform Window defaults.

A sample .*cdsinit* file included with the software contains examples of statements to copy into your own .*cdsinit* files. It has very detailed comments about command usage. This sample is located at <*install\_dir>/tools/dfII/cdsuser/.cdsinit*. An additional sample .*cdsinit* file exists for analog designers at <*install\_dir>/tools/dfII/samples/artist/cdsinit*.

### **The Installation Path**

The Design Framework II software product hierarchy is discussed in detail in the *Cadence Design Framework II Configuration Information* guide.

Introduction to ADE 5.0

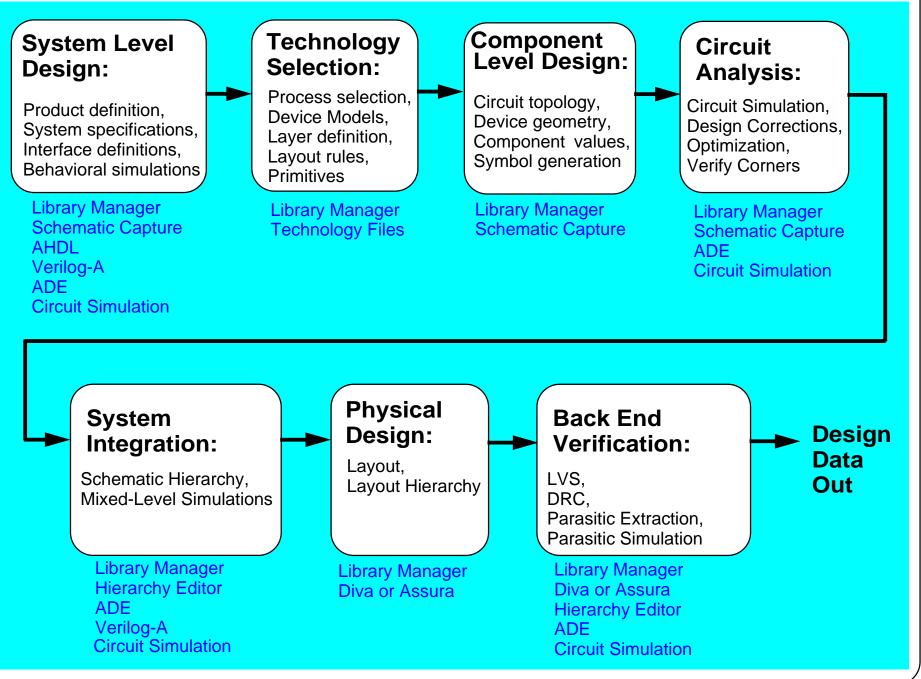

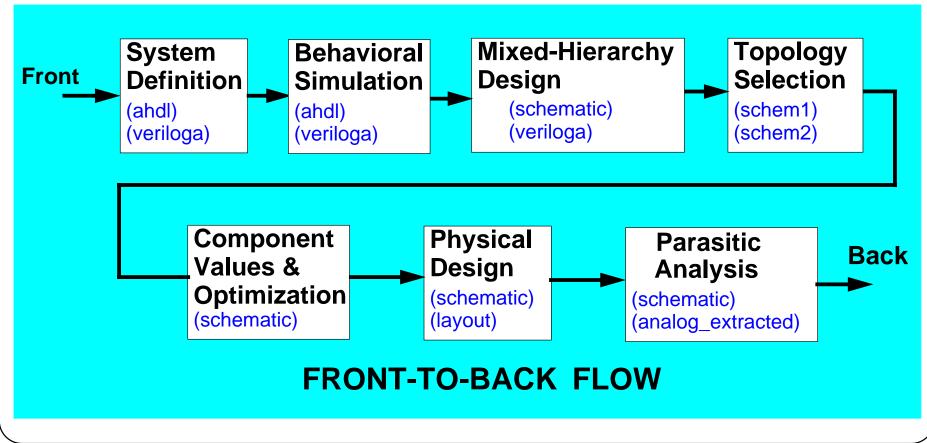

## IC Design Flow, Front to Back

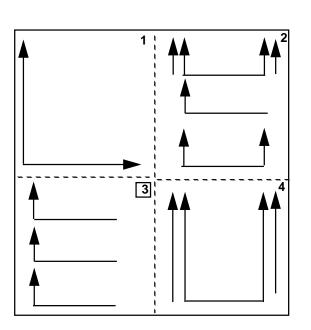

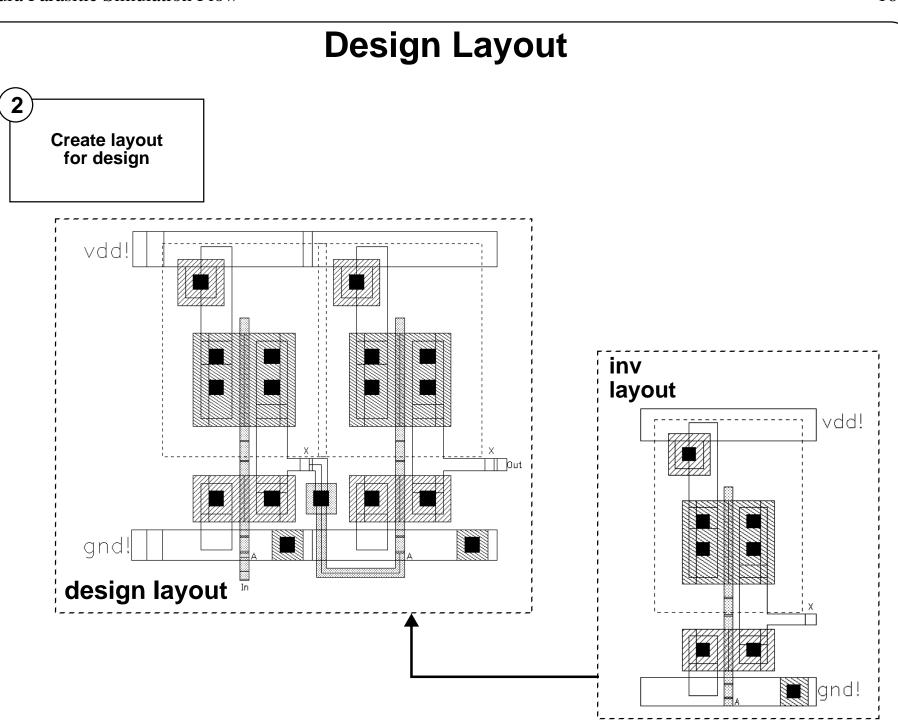

### **IC Design Flow, Front to Back**

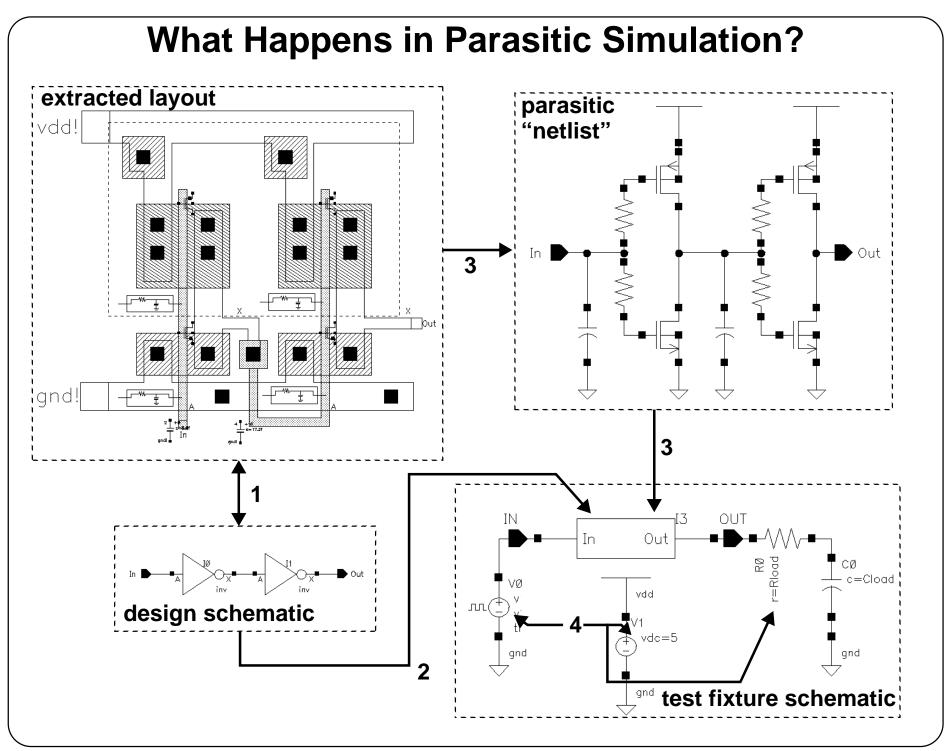

The graphical flow above shows a Front to Back design flow for integrated circuits or related system design. The blocks show the major steps or design categories. The text below each block shows the software tools used in the corresponding design steps.

- At the front end, the product, device or system is defined. The system-level specifications are used for behavioral simulation of the system.

- A fabrication process or technology is selected.

- A schematic of a specific block is captured.

- The design of the circuit is simulated. If needed, the circuit is redesigned to achieve specified goals.

- The circuit is integrated into a hierarchy. The hierarchy is then simulated.

- Physical design or layout capture of the circuit is completed. The layout of the hierarchy is then completed.

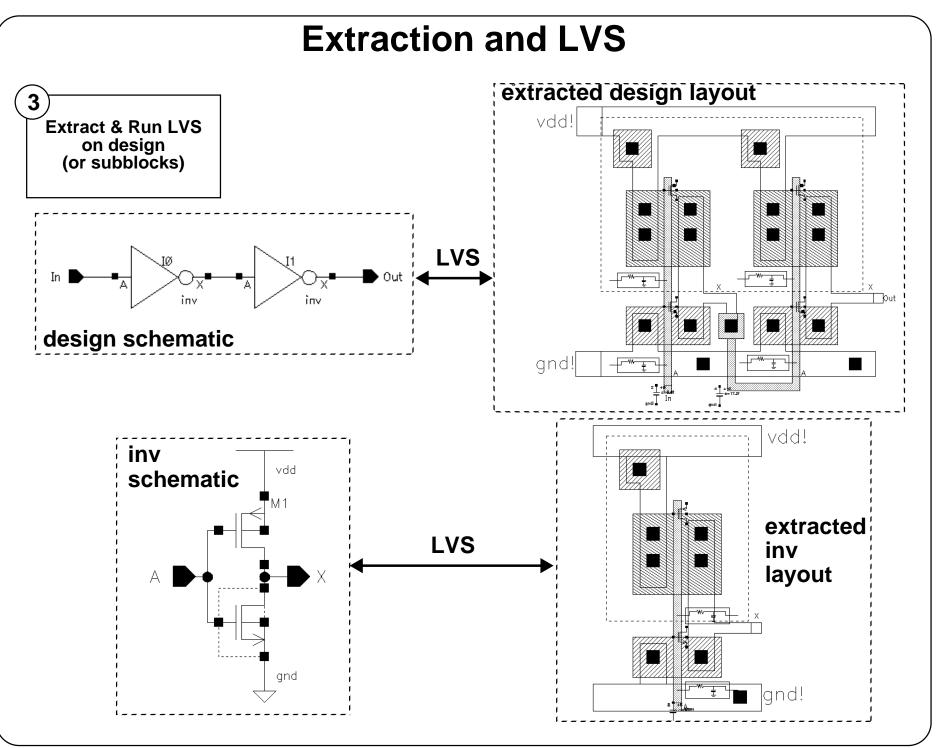

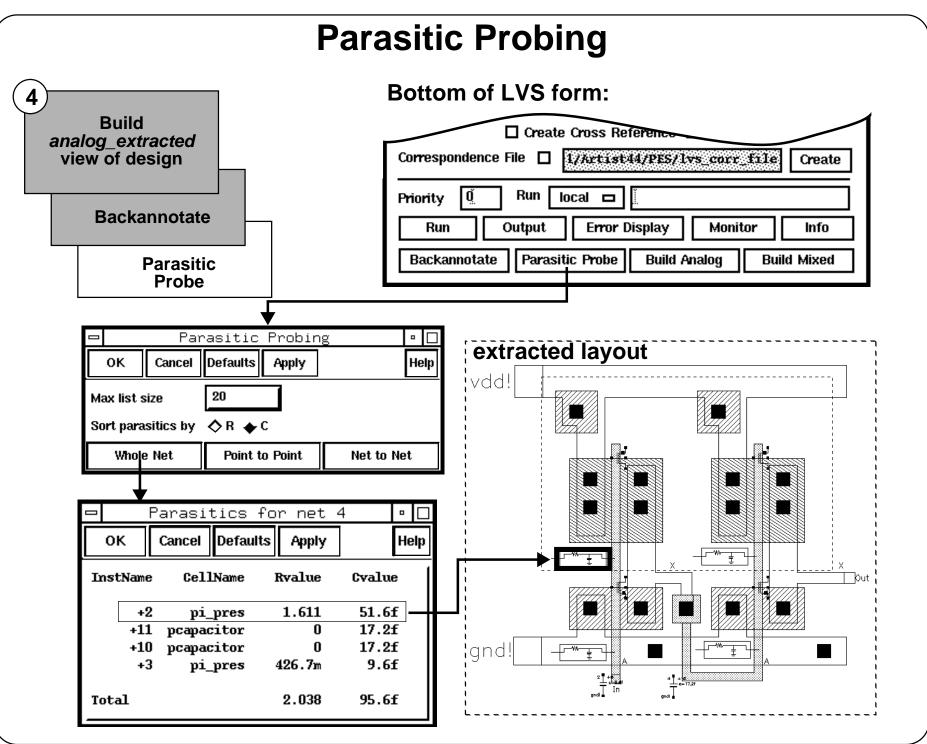

- Back end verification of the layout includes design rule checks, layout versus schematic checks, and parasitic extraction. The extracted parasitics are "backannotated" to the schematic for parasitic simulation using the circuit simulation software.

## **The Library Manager**

The Library Manager is a graphical data management tool.

| — Library Manager<br>File Edit View Design Manag                                                                                                 |                                                                                                                                                                                                                  | usr1/tim/ade500/adelabic5 |                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------|

| Show Categories Show F                                                                                                                           |                                                                                                                                                                                                                  |                           | Object<br>Sensitive |

| InhConn<br>aExamples<br>analogLib<br>basic<br>cdsDefTechLib<br>functional<br>sample<br>solutions<br>training<br>A library in<br>the cds.lib file | VCO<br>LF<br>PD<br>PLL<br>RSFF<br>VCO<br>ampv<br>control<br>controlv<br>diodev<br>foldedCascode<br>inv<br>invv<br>my_nor2<br>mydiode<br>nand2<br>nand2v<br>peakDetectv<br>peakTestv<br>schmitt<br>supply<br>test | Image: Status             | Menus               |

| Messages                                                                                                                                         |                                                                                                                                                                                                                  |                           |                     |

### **The Library Manager**

The Library Manager provides a convenient way to browse libraries containing cells and cell views. The most common use is to display the contents of libraries graphically. Other functionality includes renaming, copying, specifying permissions for, creating categories for, deleting, and viewing properties of design data. Use the Library Manager to create cells and views, to edit or read a design, and to access the design manager.

The illustration above shows a fully expanded library. Initially, the Library Manager lists only the library names that are set in the *cds.lib* file. This file contains the paths to the libraries used in the design session, including example libraries provided by Cadence, such as *analogLib* and *basic*.

Expand design data with Object Sensitive Menus (OSM) or with the mouse. To expand data, point at the word that represents the data in the Library Manager and choose the appropriate mouse button or menu command.

```

Introduction to ADE 5.0

```

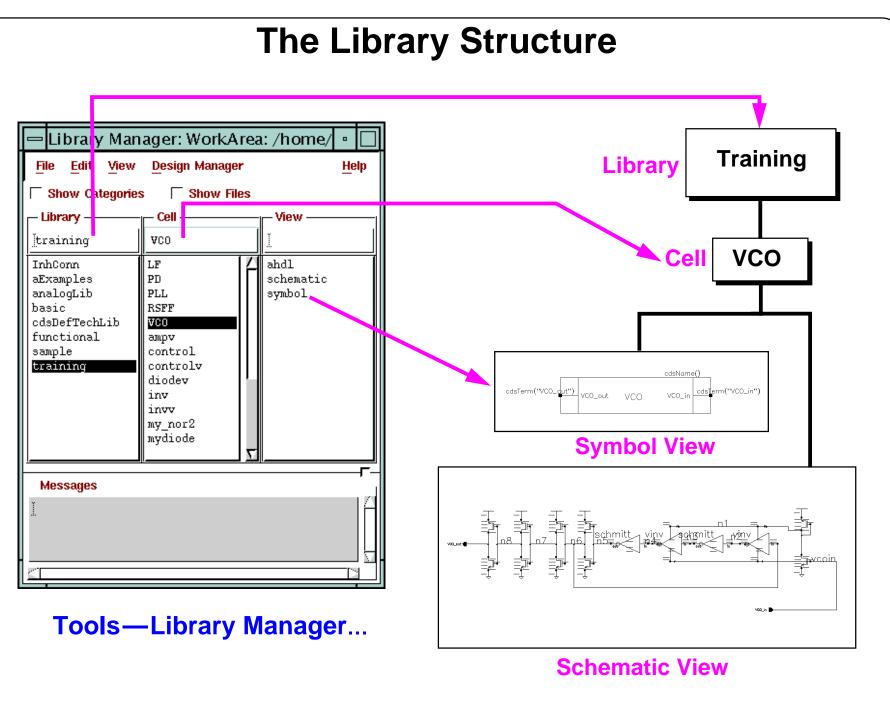

### **The Library Structure**

■ Library

A *library* is a collection of cells. The library also contains all the different views associated with each of the cells. **Reference** libraries typically contain well-characterized cells that can be instantiated in many different designs. Examples are the *analogLib* and *basic* libraries. **Design** libraries contain cells currently under development by a particular user, group, or for a particular design project.

• Cells

A *cell* is a logical component in your library. It can be a building block such as a *VCO* or *amplifier*. It can also be the top level chip name.

Views

A *view* is a particular representation of a cell such as a *layout*, *symbol*, or *schematic*. An application tool, such as *Composer-Schematic*, creates a view. Although a chip can include many levels of cell hierarchy, none of the hierarchical complexity is reflected in the libraries.

A library is a flat collection of cells. Details of the design hierarchy exist inside the views that contain instances of other cells. The library treats all cells the same.

## **Creating a New Library**

In the CIW or the Library Manager, select File—New—Library.

| _                                            | - New Library |                                        |       |                                                                                                                                                                                                                                                                                               |  |

|----------------------------------------------|---------------|----------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ок                                           | Cancel        | Defaults                               | Apply | Н                                                                                                                                                                                                                                                                                             |  |

| Library                                      |               |                                        |       | Technology File                                                                                                                                                                                                                                                                               |  |

| CORNER<br>CSurf<br>MDL1ab<br>Mode1s<br>OCEAN | S             | (<br>b <b>rary dire</b> d<br>00/ade1ab |       | If you will be creating mask layout of<br>other physical data in this library, you<br>will need a technology file. If you plat<br>to use only schematic or HDL data,<br>technology file is not required.<br>Compile a new techfile<br>Attach to an existing techfile<br>Don't need a techfile |  |

- Specify the library name and path.

- Specify the design manager to use.

- For Physical Design and Verification, specify the ASCII technology file or technology file library to be attached to the new library.

The new library is entered into the *cds.lib* file.

### **Creating a New Library**

When creating library, use a form to specify the library name and path, the design manager to use, and the technology file to attach to the library.

Technology File Contents

The *technology file* is a large data file that specifies all of the technology-dependent parameters associated with that particular library. Design rules, symbolic device definitions, and parasitic values are some of the technology-specific parameters common to all cells in a library.

■ *cds.lib* File

The software automatically updates the *cds.lib* file when creating a library through the CIW's **File**—**New**—**Library** command, when copying one library to another name, or renaming a library. This file contains the paths to all of the libraries used in the design session, and can be accessed through CIW's **Tools**—**Library Path Editor** command.

Introduction to ADE 5.0

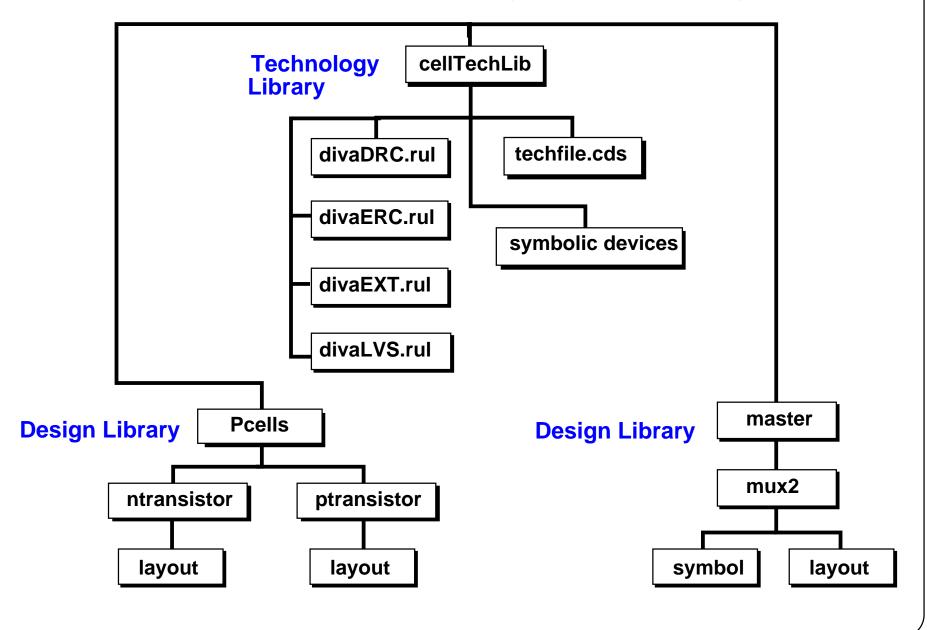

### **Shared Technology Library**

This example shows several libraries sharing the same technology file library.

### **Shared Technology Library**

Share technology file information between different libraries. Create a technology file library and attach your design libraries to the technology file library. Use the **Technology File**—Attach To command in the CIW to attach the design library to the technology file library. Sharing a technology file library with other libraries share the same Diva<sup>®</sup> rules, layer information, and symbolic devices amongst a group of libraries. Sharing a technology file can help reduce the size of the design libraries, because the technology information is stored at only one location.

■ *techfile.cds* file

The *techfile.cds* file contains the binary technology file. This file name must be called *techfile.cds*.

Diva Rules

The Diva rules are stored as separate ASCII files. For each type of rule (DRC, Extraction, ERC, and LVS), there is a Diva rules file.

■ Symbolic Devices

The symbolic devices such as contacts, pins, transistors, and wire information can be shared between libraries.

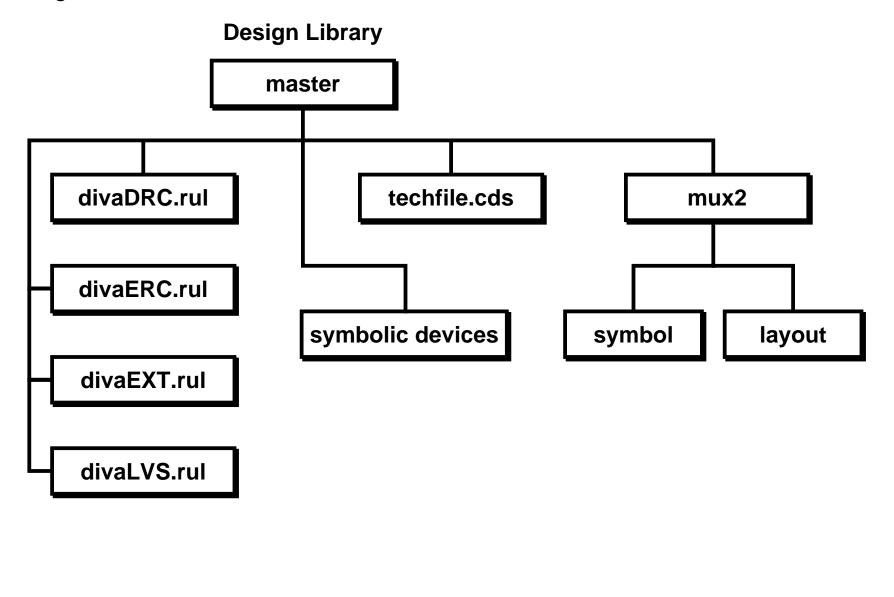

# **Technology File Stored in the Design Library**

This example shows a technology file being stored inside a design library and not being shared with other libraries.

## **Technology File Stored in the Design Library**

A library can have its own technology file information that is stored inside of the library.

## **Design Data Management**

- Version control

- Configuration management

- Access control

- Release process

#### **Design Data Management**

Manage your design data using a suitable data management system. The following are some of the benefits of design management:

- Maintaining multiple versions of design data

- Releasing correct versions of designs

- Preventing accidental deletion of someone else's design in a team environment

- Tracking or monitoring design status

- Isolating "what-if" design scenarios

- Effectively sharing stable design data

- Easily rolling back to a previous state of a design

The Cadence Team Design Manager (TDM) is our design data management system. Your system administrator or CAD support group must decide what data management system (if any) your projects will use.

Introduction to ADE 5.0

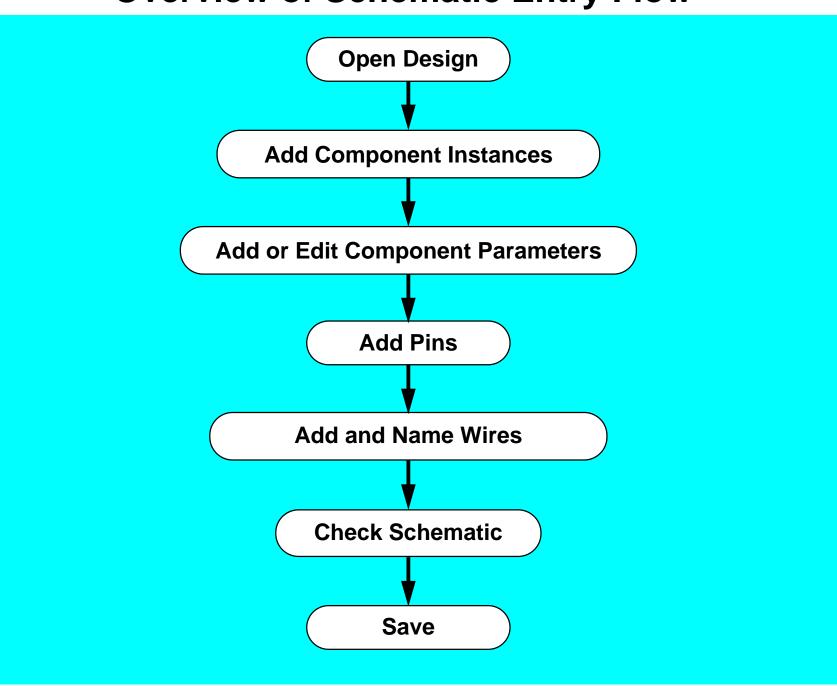

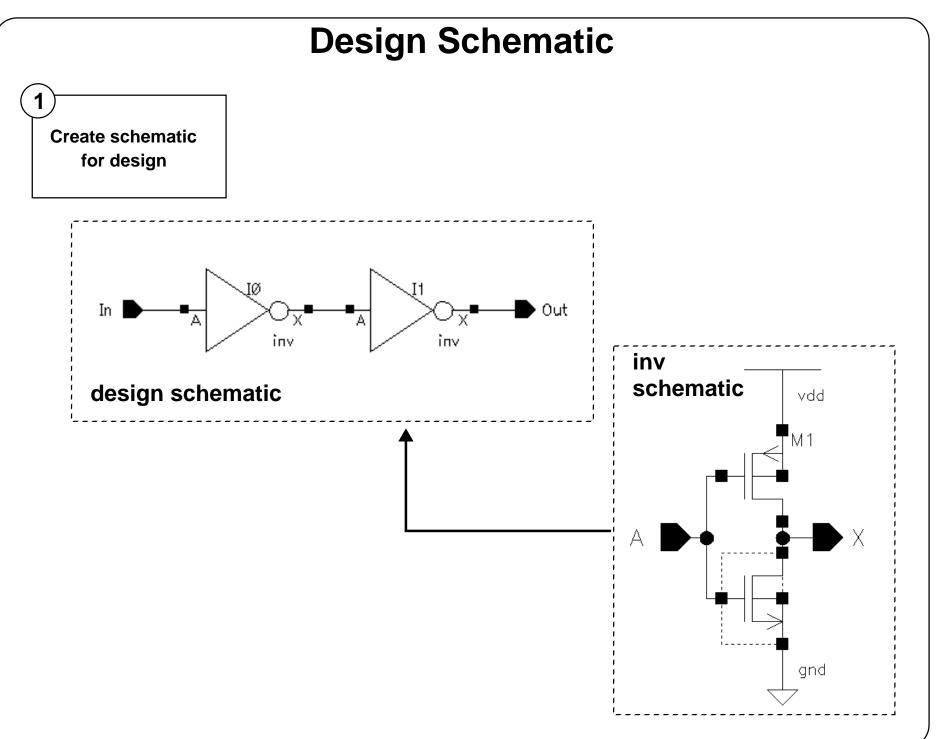

### **Overview of Schematic Entry Flow**

Perform the following steps when creating a schematic:

- 1. Open the design.

- 2. Add component instances by placing cellviews from libraries.

- 3. Add or modify component parameters.

- 4. Add pins to indicate connections outside of this schematic.

- 5. Connect the components and pins.

Use wires to do this. This step also includes giving meaningful names to signals in the design.

- 6. Check the design to ensure that it is correct.

- 7. Save the design.

Note: These steps shall be discussed in detail in the next module.

Introduction to ADE 5.0

1-41

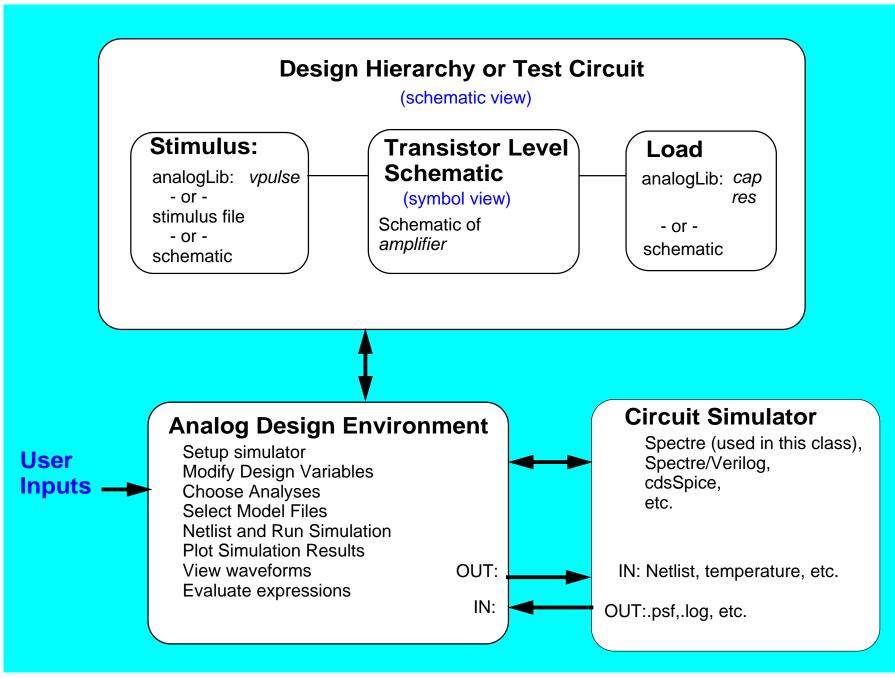

### **Overview of Circuit Simulation**

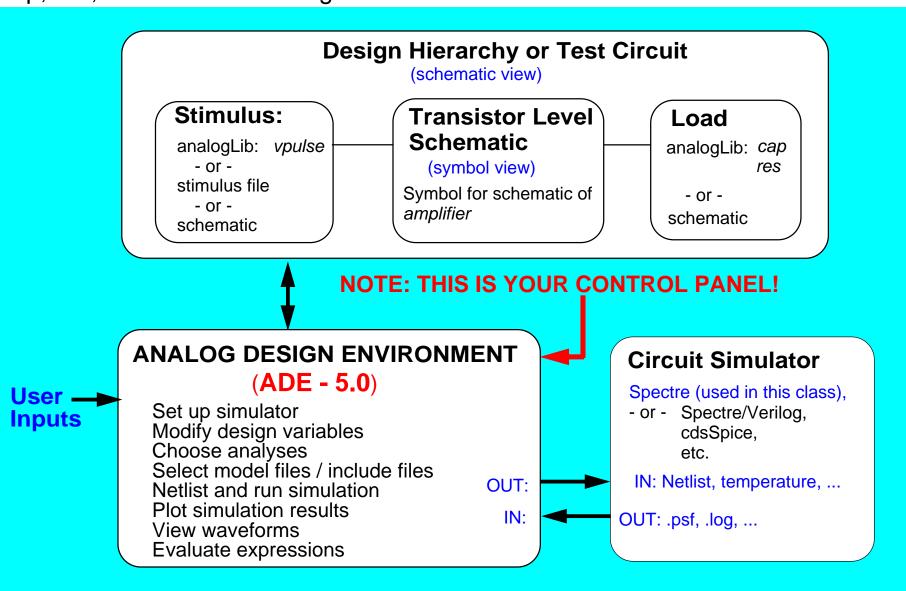

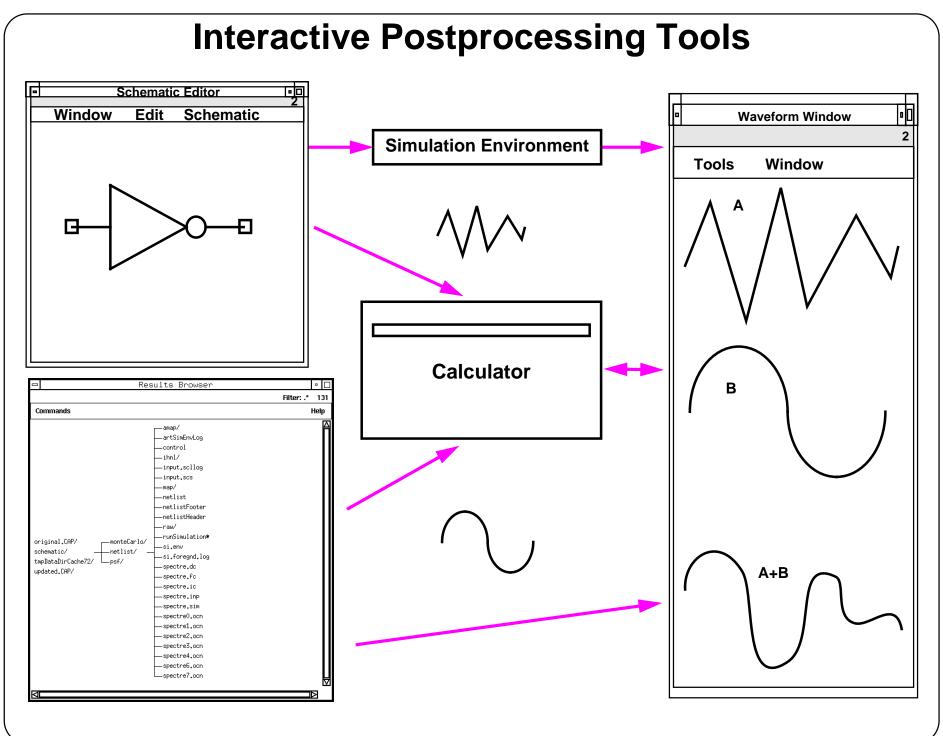

The block diagram above shows an overview of the circuit simulation process.

- The circuit schematic is captured or edited.

- A symbol of the schematic is placed in a hierarchy or test circuit schematic.

- The Analog Design Environment is started.

- The user provides input to the Analog Design Environment to set up and control what information is netlisted and then sent to the circuit simulator.

- The user used the Analog Design Environment to run the circuit simulator.

- The user selects the information to be printed, plotted, or to be analyzed.

- The user modifies the setup or edits the schematic for the next simulation.

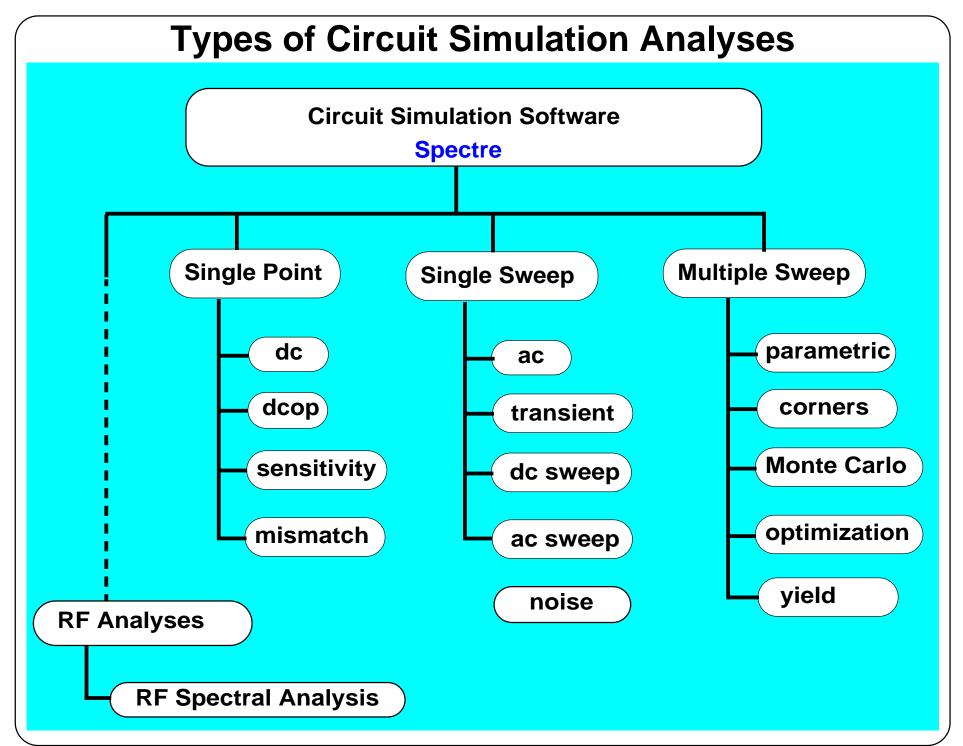

# **Types of Circuit Simulation Analyses**

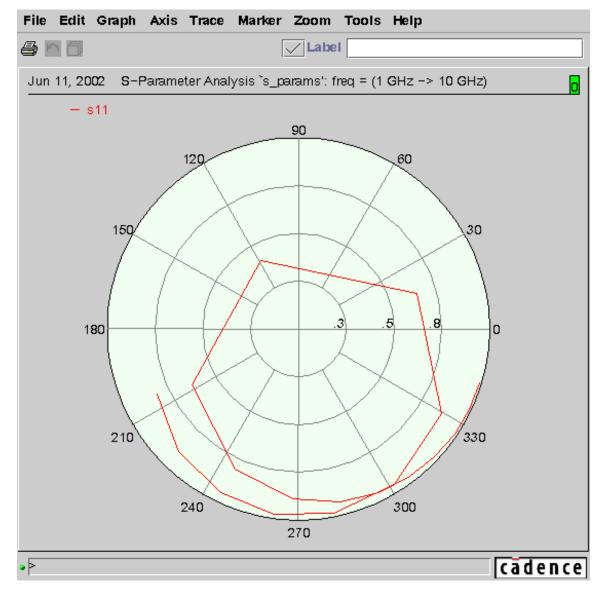

The diagram shows the variety of analyses available with analog circuit simulation.

Single-point analyses often include the steady state **dc** solution of the circuit. The operating point **dcop** solves the operating point device parameters and low frequency gain of the circuit.

Single-sweep analyses often include **ac** and **transient** analysis. The **ac** analysis is a frequency sweep of the circuit. The **transient** analysis is a time sweep of the circuit operation to a time domain stimulus. A **dc sweep** analysis is a multiple point dc analysis performed while stepping a parameter such as temperature, design variable, or a model parameter. Solving the dc gain of an amplifier as a function of temperature is often called a **temperature sweep**. Solving the gain of an amplifier as a function of a model parameter is called a parametric sweep. It is also possible to sweep the **ac** gain of an amplifier at a specified frequency of the amplifier over temperature. This is called an **ac temperature sweep**.

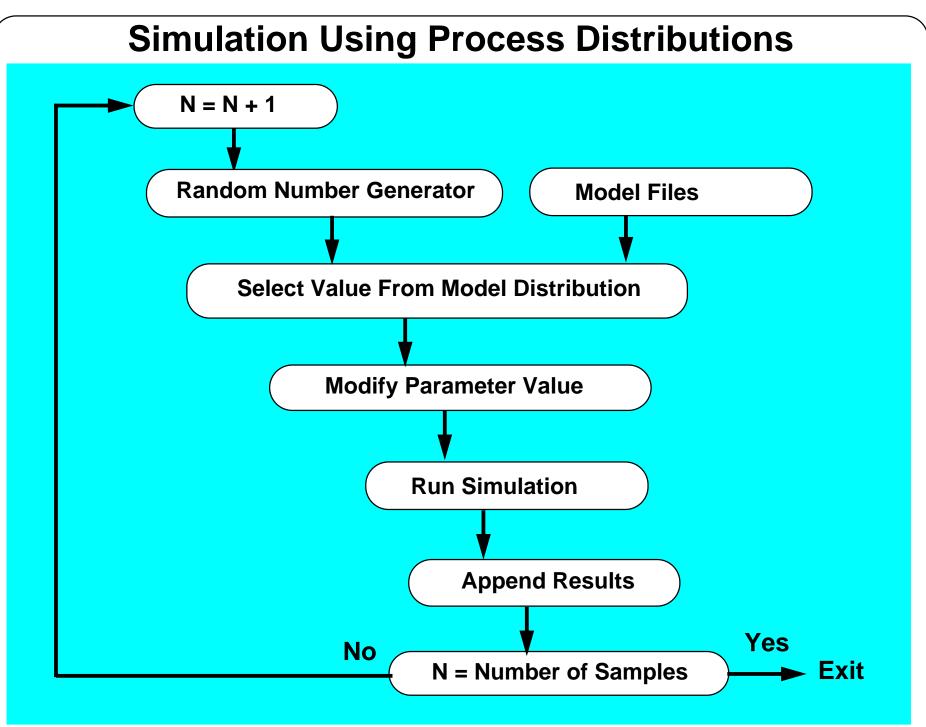

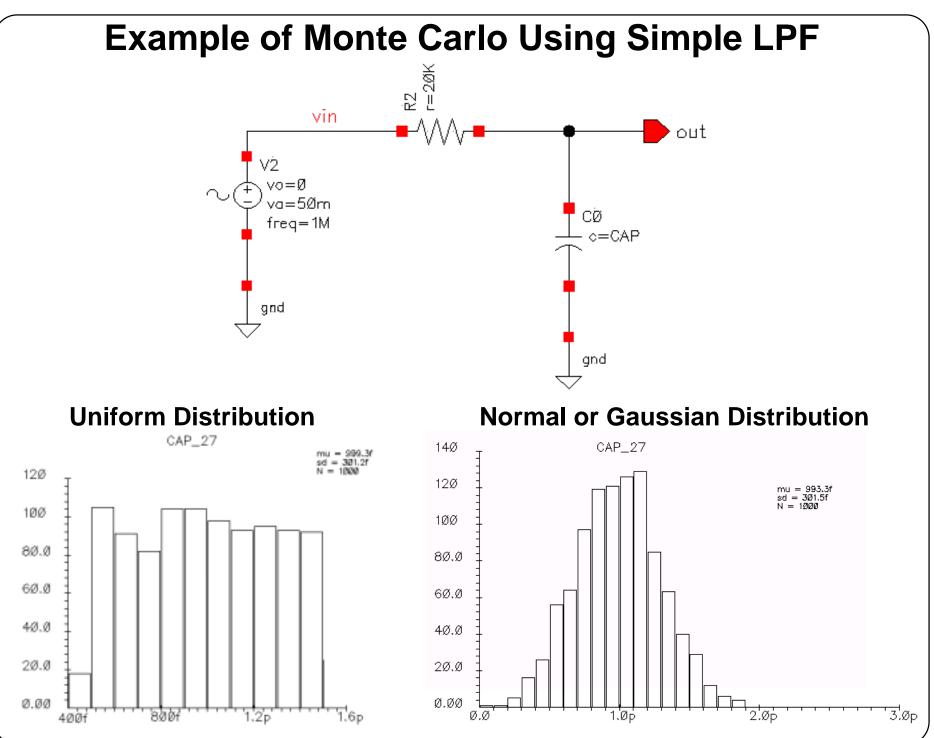

Multiple sweep analyses refer to sweeping one variable and then stepping another variable between successive sweeps. In **parametric** analysis, the two or more variables are altered at specified intervals. In the **Corners** analysis, variables are specified at named corners. In the **Monte Carlo** analysis, the parameters are altered using random number generators and a specified distribution. In **optimization** analysis, the parameter are altered using the results of the previous simulation and a search algorithm.

The Analog Design Environment and the Spectre circuit simulator are capable of performing the analyses shown above. In addition, the Spectre circuit simulator can perform special steady state **ac spectral analysis** on RF waveforms. These analyses are discussed in the Spectre RF classes.

# Summary

In this module we discussed:

- Course objectives

- Course outline

- Class schedule

- Getting Help, including CDSDoc

- Design Framework II environment

- Using forms

- Creating a library

- Creating cells and cell views

- Overview of schematic capture

- Overview of circuit simulation in the Analog Design Environment

- Types of simulation analyses

### Summary

In this module we provided an introduction to the class, including:

- Class objectives

- Class schedule

- Online documentation

This module also provided discussion on the Design Framework II environment, including:

- Starting DFII with *icfb*, *icms*, or *msfb*.

- The Command Interpreter Window (CIW)

- Use of forms

- Front to Back design flow using Design Framework II

- Overview of schematic capture

- Overview of circuit simulation in the Analog Design Environment

- Types of simulation analyses

#### Lab 1-1 Getting Started

Lab 1-2 Top-Down System Modeling

#### Labs

## **Module 2: Schematic Entry**

#### **Topics in this module**

- The schematic capture flow

- Creating a schematic view

- Contents of a schematic

- Adding component instances

- Adding pins

- Adding wires

- Editing object properties

- Using Accelerator keys (also known as bindkeys) and schematic window icons

- Checking the schematic for errors

- Symbol generation and editing

- Using a design hierarchy

### **Terms and Definitions**

| library        | A set of design directories that includes 'cells' and 'cellviews'.       |

|----------------|--------------------------------------------------------------------------|

| Library Manage | A Cadence tool that allows user to browse and edit a design library.     |

| Composer       | Schematic editor and symbol generation tool in DFII.                     |

| cell           | A basic unit of a design hierarchy described by cell views.              |

| cell view      | A specific view of a cell that includes schematic, symbol or layout.     |

| instance       | A uniquely named placement of a symbol onto a schematic.                 |

| pin            | A connection point on a schematic and symbol used for accessing signals. |

| bindkey        | A predefined key on the keyboard that invokes a preselected command.     |

Schematic Entry

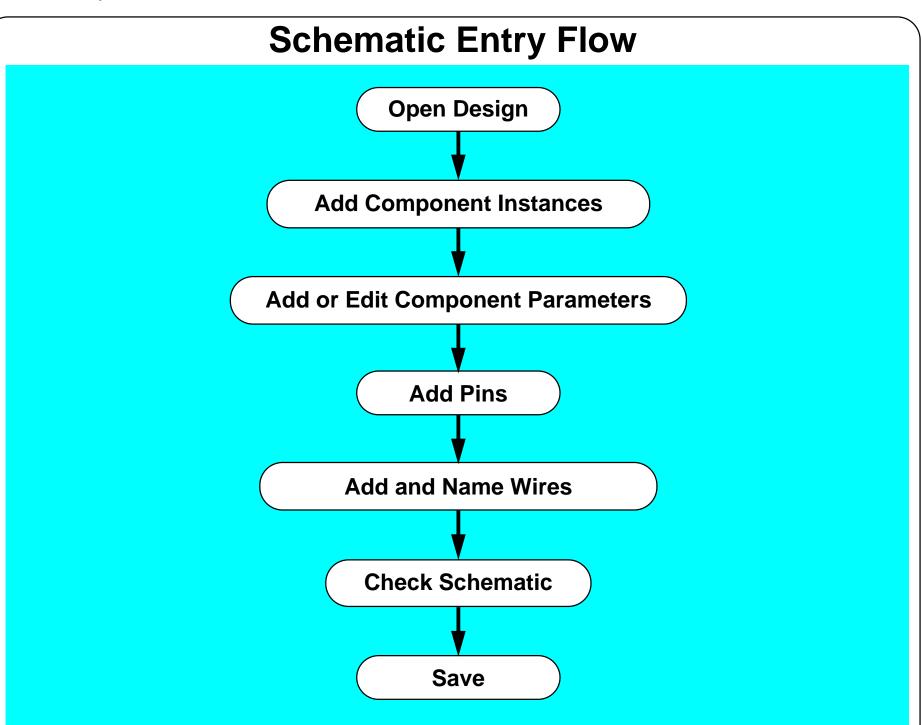

### **Schematic Entry Flow**

Perform the following steps when creating a schematic:

- 1. Open the design. Use the CIW or Library Manager tool.

- 2. Add component instances by placing cellviews from libraries.

- 3. Add or modify component parameters.

- 4. Add pins to indicate connections outside of this schematic.

- 5. Connect the components and pins.

Use wires to do this. This step also includes giving meaningful names to signals in the design.

- 6. Check the design to ensure that it is correct.

- 7. Save the design.

Schematic Entry

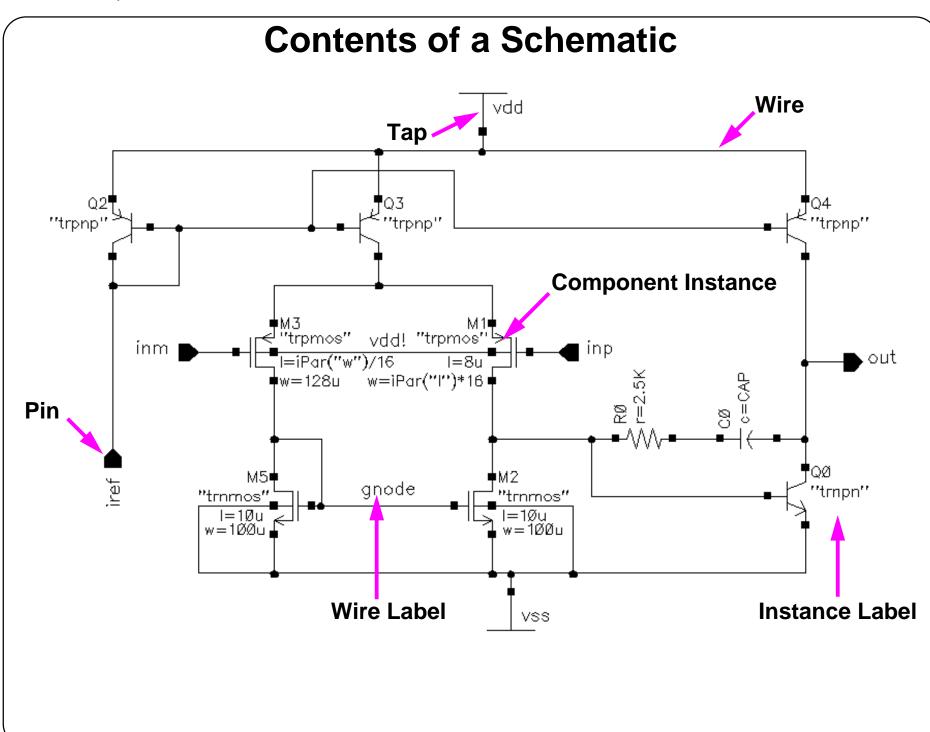

### **Contents of a Schematic**

- Component instances represent instantiations of other cellviews in this cellview.

- Instance labels display component information in the design entry window.

- Pins can be inputs and outputs of a schematic or connection point when an instance is placed in another cellview.

- Wires can be drawn between pins to connect them.

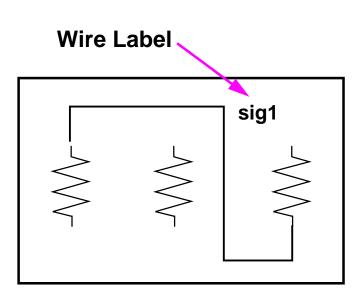

- Wire labels provide meaningful signal identifiers for simulation results analysis.

- Analog taps and sources can be included directly in the design.

## **Creating a New Cellview**

In the CIW or Library Manager, select File—New—Cellview.

| -                                           | Crea   | ate New          | File            |      |  |                      |

|---------------------------------------------|--------|------------------|-----------------|------|--|----------------------|

| ок                                          | Cancel | Defaults         |                 | Help |  |                      |

| Library Na                                  | ame 🗌  | mylib 🗆          | ו               |      |  |                      |

| Cell Name                                   | a      | mplifier         |                 |      |  | Default View Name    |

| View Nam                                    | ie s   | chemati <u>č</u> |                 |      |  | subject to override. |

| Tool                                        | Co     | mposer-S         | chematic        | :    |  | Select:              |

| Library path file                           |        |                  | Composer-Schema |      |  |                      |

| me/aztec/445/aads/Artist445/cds.li <u>k</u> |        | -                |                 |      |  |                      |

- Specify the Library Name, Cell Name, View Name, and Tool to use. The path to the *cds.lib* file will appear in the form and is not editable.

- Modify the Tool field to create a layout, verilog, symbol, schematic, vhdl, or ahdl view.

For an ADE schematic, select **Composer-Schematic** from the Tool cyclic field

#### **Creating a New Cellview**

Create a new cell views from the Library Manager or CIW.

Specify the Library Name, Cell Name, View Name, and Tool to use. The path to the *cds.lib* file will appear in the form and is not editable.

Modify the Tool field to create a *layout*, *verilog*, *symbol*, *schematic*, *vhdl*, or *ahdl* view. For a schematic, use *Composer-Schematic*. This will automatically enter *schematic* into the View Name text field.

####

Although *schematic* is automatically entered into the View Name text field by default, you have the option to name the view anything you want. For example, the View Name may be altered to *schem1*, and the process repeated for *schem2*. As such, there are two or more schematic views for the same cell name. This allows parallel circuit designs within the same cell name. A common symbol for both schematics is then used within the hierarchy, until the final schematic is selected. This feature is useful in exploratory designs where the final circuit topology has not yet been finalized.

# **Adding Component Instances**

Select Add—Instance or press the i key to display the Add Instance form.

- Attach multipliers to values. Enter 1k (not 1 k) so that k is not mistaken as a variable.

- Parameter units, such as *ohms*, are implicit.

|                                 | - Add Instance |               |          |           | $\neg$  |             |       |

|---------------------------------|----------------|---------------|----------|-----------|---------|-------------|-------|

|                                 | Hide           | Cancel        | Defaults |           |         | H           | elp   |

|                                 | Library        | analogL.      | ih       |           |         | Browse      | ]     |

|                                 | Cell           | re <u>š</u> i |          |           |         | ]           |       |

|                                 | View           | symbol        |          |           |         |             |       |

|                                 | Names          | R₫            |          |           |         | ]           |       |

|                                 | Array          | F             | Rows     | Ľ.        | Columns | 1           | ╹║    |

| Use these buttons while placing | Rotat          | e             | Sic      | leways    |         | Upside Down | ]     |

| components to                   |                |               |          |           |         |             | ╢     |

| control orientation.            | Resistan       | ce            |          | 1K Ohmsį́ |         |             |       |

|                                 | Tempera        | ture coeffi   | cient 1  | ·         |         |             |       |

|                                 | Tempera        | ture coeffi   | cient 2  |           |         |             |       |

|                                 | Model na       | me            |          |           |         |             |       |

|                                 | Length         |               |          |           |         |             |       |

|                                 | L              |               |          | 1:        |         |             | التار |

## **Adding Component Instances**

Design components are generally instances of a *symbol* cellview and might be design primitives. Here are some properties associated with design component instances:

| Parameter     | Example Value |

|---------------|---------------|

| Library Name  | analogLib     |

| Cell Name     | res           |

| View Name     | symbol        |

| Instance Name | R2            |

The Instance Name is assigned automatically, unless explicitly specified.

Find analog design primitives in the *analogLib* library. This library is included wherever the Analog Design Environment software is installed in the path <*install\_dir>/tools/dfII/etc/cdslib/artist*. Include this path in your library search path to use *analogLib* components.

The system prompts for component parameters when instantiating the components. Attach multiplier suffixes, such as  $\mathbf{k}$  for 1000, to numerical quantities.

Use the **Rotate**, **Upsidedown**, and **Sideways** buttons to change the orientation of your components as they are placed in the schematic.

# **Updating Design Objects**

- Select Edit—Properties—Objects or bindkey q to start the form. The Next and Previous buttons highlight single objects in a selected set.

- Use **Design**—**Renumber Instances** to renumber instances in a design.

|                           |                  | Edit Obje                    | ect Propert    | ies   |         |

|---------------------------|------------------|------------------------------|----------------|-------|---------|

| OK Can                    | cel Apply [      | Defaults Previ               | ous Next       |       | Help    |

| Apply To<br>Show          |                  | rrent 📼  insta<br>tem 🔳 user | nce 🗖          |       | A       |

|                           | Browse           | Reset Insta                  | ance Labels Di | splay |         |

| Pro                       | perty            |                              | Value          |       | Display |

| Lib                       | rary Name        | analogLibį́                  |                |       | off 🗖   |

| Cel                       | Cell Name        |                              |                |       | off 🗖   |

| Vie                       | View Name        |                              |                |       | off 🗖   |

| Ins                       | Instance Name Rǚ |                              |                | off 🗖 |         |

|                           |                  | Add                          | Delete         | Mod   | ify     |

| CD                        | F Parameter      |                              | Value          |       | Display |

| Resistance                |                  | 1K Ohms                      | [              |       | off 🗖   |

| Temperature coefficient 1 |                  |                              | off 🗖          |       |         |

| Temperature coefficient 2 |                  |                              |                |       |         |

| Model name off 🗖          |                  |                              | off 🗖          |       |         |

| Length                    |                  | •<br>                        |                |       |         |

| 😑 Renumber Instances |         |          |      |  |

|----------------------|---------|----------|------|--|

| ОК                   | Cancel  | Defaults | Help |  |

| Verbose              |         |          |      |  |

| Scope                | cellvie | w 📼      |      |  |

#### **Design**—Renumber Instances

### **Updating Design Objects**

You can either update single or multiple objects in a selected set. Use the *Next* and *Previous* buttons on the Edit Object Properties form to scroll through a set of selected objects and update them. Only one object at a time will highlight in the schematic window. It is possible to modify most quantities that appear on the form.

The most common changes concern components parameters, pin name, and pin direction.

In addition, use the Stretch, Copy, Move, Delete, and Rotate commands to update your design. These commands are located under the **Edit** menu in the schematic window. To display an options form that is associated with any of these commands, use the **Cmd Options** icon or press the **F3** key while these commands are active.

Use the Renumber Instances form to renumber instances. This form renumbers component names in sequential order to make it easier to track component totals. In addition, adding and deleting components in a schematic during the design process can leave components labeled improperly.

Note: The renumber sequence depends on the order that the symbols were added to the schematic.

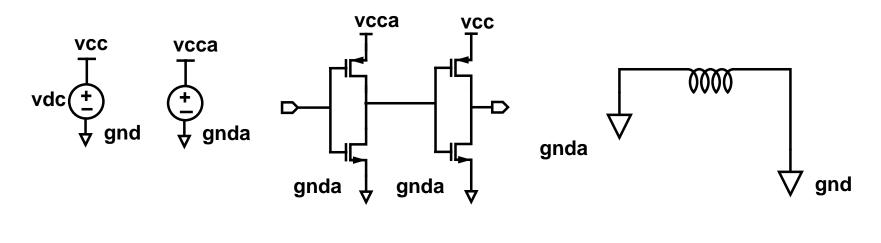

# **Adding Sources and Ground**

#### Sources, taps, and grounds are instances of cells.

Sample source cells are in the *analogLib* library.

- Choose from independent, dependent, and piece-wise linear (PWL) sources.

- Choose tap and ground cells, which are used to establish global nets.

- An instance of the cell *gnd* is required in the design for DC convergence.

## **Adding Sources and Ground**

#### ■ Ground

Always include the symbol *gnd* (found in the *analogLib* library). Analog simulators require that all nodes in the circuit must have a DC path ground. This would be represented as *node 0* in the Cadence SPICE circuit simulator, for example. Use other ground symbols, such as *gnda*, for a ground that is connected to the reference ground through an analog circuit.

#### ■ Voltage Sources

Include all of your DC and transient voltage and current sources in the schematic. There are many types of voltage sources in *analogLib*. For example, some of the independent voltage sources are vdc, vsin, vpulse, vexp, vpwl, and vpwlf. Each source has a current equivalent that begins with the letter i. There are also equivalent dependent sources.

All sources generate input waveforms except for *pwlf* sources, which stimulate a circuit using a text file of data tables. It is not necessary to include sources in the schematic, although this is often convenient. Attaching a stimulus file to the final netlist is discussed in the analog simulation section of this course.

#### ■ Voltage Taps

Use tap symbols to transfer voltages and currents throughout the design without using wires. Voltage tap symbols, such as *vcc*, *vdd*, *vcca*, and *vccd*, are in the *analogLib* library.

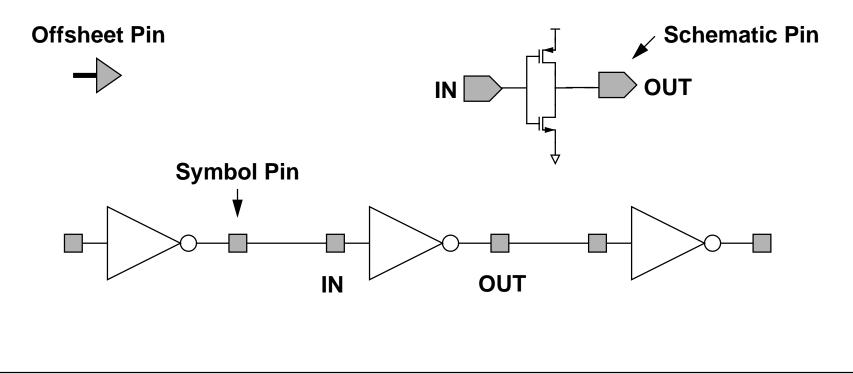

## Pins

Pins have a user-defined *Name* and a *Direction* (input, output, or input/Output). Pins are one of three *types*:

- Schematic pins provide ports to a schematic.

- Symbol pins provide ports to a symbol representing a schematic, and are connection points to the symbol in a hierarchical design.

- Offsheet pins are used in large designs without hierarchy.

Pin names and directions must match in all cellviews of a cell.

### Pins

For analog designers, pins have two primary functions:

- Pins represent connection points between different cell views such as schematic, symbol, and layout representations. Using named pins identifies equivalent input, output, and I/O ports throughout the design environment.

- Pins provide connection points for objects that are hierarchically instantiated.

#### **Pin Properties**

Pins have a pin name, pin type, and pin direction. These should be consistent throughout your design.

#### **Multiple Sheet Design with Offsheet Pins**

The *Virtuoso Schematic Composer User Guide* manual includes a section on multiple sheet design methodology and information on the *offsheet* pin type. You can get other help for the Composer software in the Cadence online help.

Pins (*ipin*, *opin*, *iopin*, *sympin*) now come from "basic" library.

#### Schematic Entry

# Wires and Wire Labels

Automatic routing is the default mode.

#### **Route Entered**

#### The System Routes

When not labeling a wire, the system names the net formed by the wires.

If the router cannot find a path between two points,

- A dotted "flight line" is placed to establish connectivity only.

- Click on intermediate points to guide the router to yield a solid line of connectivity.

- Use the Cmd Options icon or F3 key to modify the wiring options.

#### Wires and Wire Labels

Draw wires between the instance pins and schematic pins to connect them. Use wide wires to indicate multiple signals on a wire, the system does not force or check this. Draw wires at any angle, but most designers frequently restrain wires to orthogonal lines.

■ Using Route Methodology

The route draw mode chooses two points in your design and then it automatically routes a wire around components. If a routed net remains dotted, it is because there was no clear routing channel. This can happen if the instances are too close or overlap the selection boxes. To solve this, move the components further apart to give a routing channel.

Route method options exist to wire together two points immediately (the default) or indicate many points to route together later in a single step. More information on route methods is included in the design entry reference documentation.

#### ■ Wire Labels

Labeling wires gives the corresponding net a meaningful name in the simulation results data. Otherwise nets are system named. There is some control over the automatically generated names, but these may not be as meaningful as custom names.

Click the **Cmd Options** icon in the schematic window or press the **F3** key to change the default wiring setup.

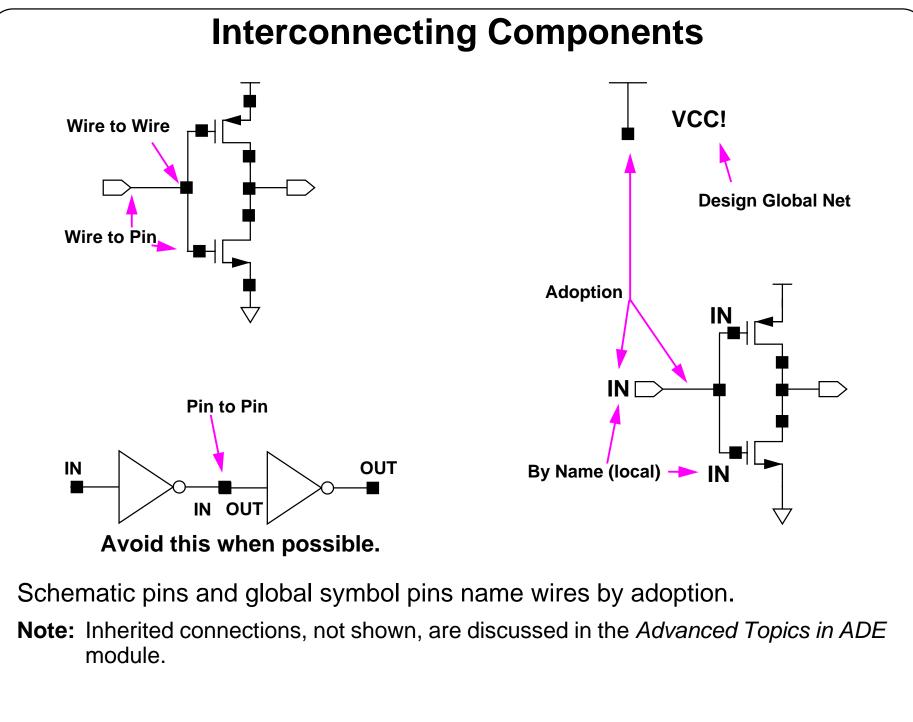

#### **Interconnecting Components**

Physical Connectivity

All physical connections are made by wire-to-pin, wire-to-wire, or pin-to-pin connections.

■ Connectivity by Name

If two wires have been labeled with the same name, they become part of the same net when connectivity is established.

#### ■ System-Assigned Names

If a net is unnamed, the system generates a name such as *net100* or *net7*. Optionally change the base name from *net* to something else. If a wire is connected to a schematic pin, then the pin name is used to name the net by adoption when connectivity is established.

#### ■ Global Nets

Any net or pin name that ends in an exclamation point will be part of a global net when connectivity is established. Global nets are automatically connected through the hierarchy without the use of wires. For example, voltage taps have symbol pin names that end in an exclamation point. If a wire is connected to a pin that has a global name, the pin name is used to name the net by adoption. This is how voltage and ground signals are propagated throughout a design.

Note: A net named *net*! is not connected to a net named *net*.

### **Schematic Checking**

During schematic checking, all of the following are performed by default:

Update Connectivity

This process associates wires and pins with logical connections called nets.

- Schematic Rules Check

- Logical checks

- Physical checks

- Name checks

- Cross-View Checker

This option checks for pin name and direction consistency between cellviews.

Select Check — Rules Setup from a schematic window to edit the rules. Disable any or all of these schematic checking features, if not needed.

## **Schematic Checking**

Schematic checking is a critical step in the design process.

Either check a single cellview or descend through the hierarchy to check all cellviews in your design.

Checking a schematic accomplishes the following:

- Update Connectivity—When connectivity is established, wires and pins in the design entry window become associated with logical connections called nets. It is necessary to correct connectivity problems prior to going on to the next design phase.

- Schematic Rules Check—This process checks the schematic with a set of rules. Access them with the **Check—Rules Setup** command from the schematic window.

The checks include:

- Logical checks, such as *Floating Input Pins* and *Shorted Output Pins*.

- Physical checks, such as *Unconnected Wires* and *Overlapping Instances*.

- Name checks, such as *Instance Name Syntax*.

- Cross-View Checker—This option checks the pin consistency between different views of the cell. Pin names and directions must match between cellviews.

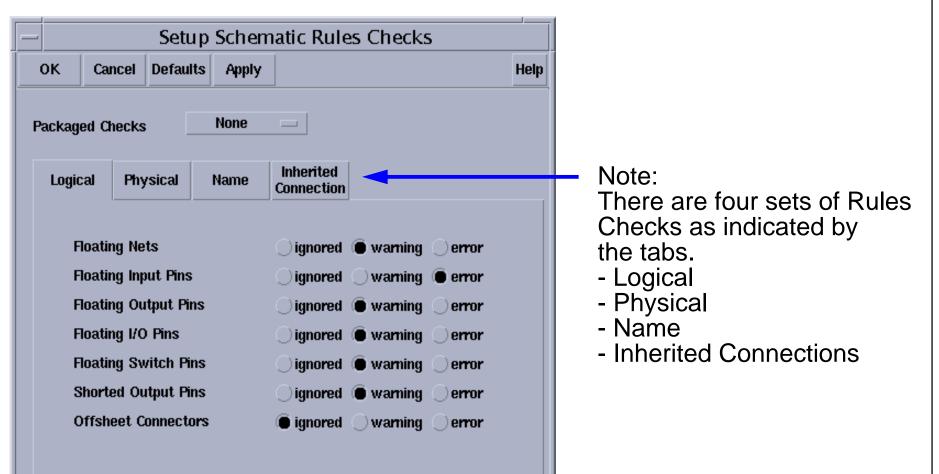

# Schematic Checking Rules

The system sets the default schematic checking rules.

The following set and selections are logical types of rules:

**Note:** *Ignored* means do not check for a condition. It is permitted to generate a netlist and run a simulation with *warnings*, but not with *errors*.

### **Schematic Checking Rules**

The Schematic Rule Checker (SRC) performs schematic syntax checks. Select and override the default values of schematic rule checks. The defaults are acceptable for most applications. Select and set the severity level for SRCs. There are three levels for each check:

| ignored | SRC does not perform the check.                                                                                                                       |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| warning | Warnings do not need to be corrected before continuing. SRC treats schematic connectivity as valid. The netlist program can still read the schematic. |

| error   | Problems must be corrected before continuing. SRC treats<br>schematic connectivity as invalid. The netlist program refuses to<br>read the schematic.  |

The checks are done for three different areas:

| Logical checks  | These checks consist of component connections that could affect the functionality of the circuit.         |

|-----------------|-----------------------------------------------------------------------------------------------------------|

| Physical checks | These checks consist of problems dealing with overlapping components, unconnected wires, and solder dots. |

| Name checks     | These checks consist of problems associated with name syntax, behavioral model syntax, etc.               |

A description of the rules is in the Virtuoso Schematic Composer User Guide.

Schematic Entry

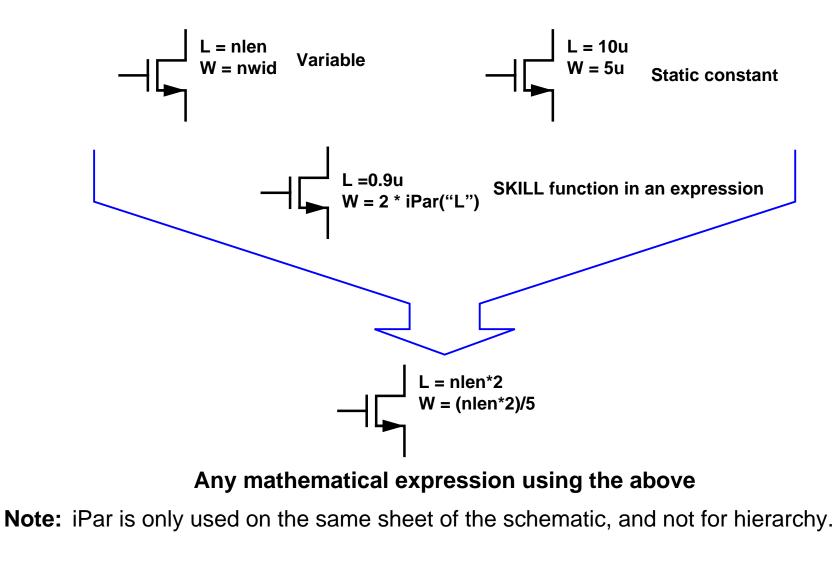

#### **Component Parameter Types**

Use user-defined functions to describe parameters.

#### **Component Parameter Types**

Some basic types are static constants, global variables, and dependent variables. Use these in combination with a mathematical expression to create parameters.

To change a value during simulation, assign a variable name. Before running simulation, set design variables. All quantities assigned the same variable name will get the same value.

Hierarchical variables, user-defined functions, and user-defined constants are discussed later.

#### **SKILL Functions**

Use built-in SKILL functions that return design parameter values and use them in expressions to set component parameters. For example, to make the width of a MOS device a function of its length. In this example, if the length of a component is defined as *L*, then the width can be set as

```

w= 2 * iPar("L")

```

to make the width of the device twice the length.

In general, the SKILL function

```

iPar("parameter name")

```

returns the value of a component parameter of the local cell.

More information on *pPar* and *iPar* is found in CDSDoc.

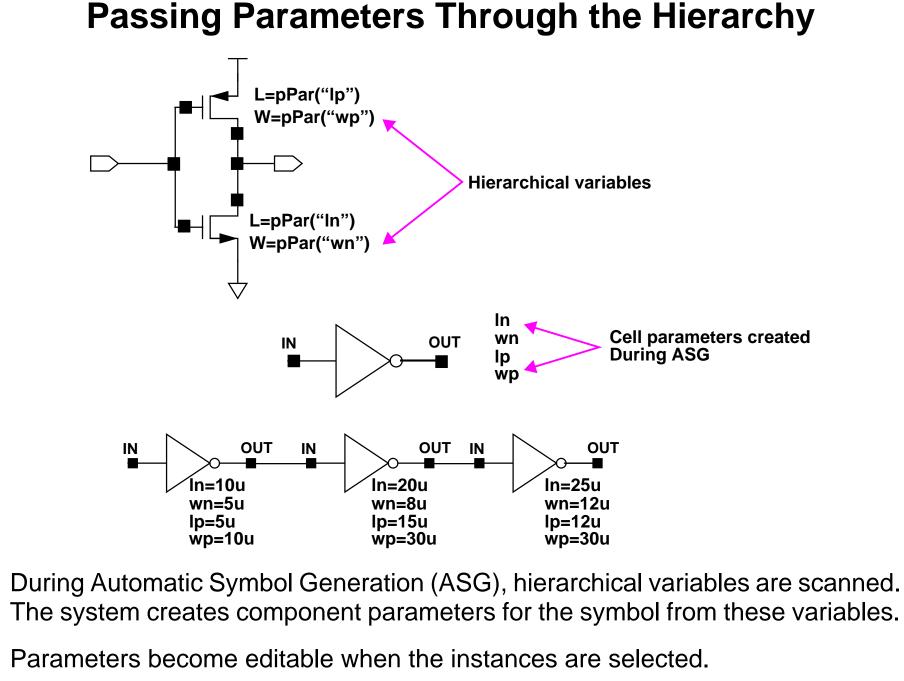

#### **Passing Parameters Through the Hierarchy**

You can place the same symbol many times and alter its schematic component parameter values at the instance level.

To accomplish this, assign expressions to schematic components using the following syntax: pPar("variable")

The value of the *variable* will be passed from the symbol level in the hierarchy to a component parameter in the schematic. Set the value of the *variable* when placing the symbol that was automatically generated from a schematic with hierarchical variables. During Automatic Symbol Generation (ASG), the system analyzes the hierarchical variables to determine what component parameters to prompt for when placing a symbol in another cellview.

#### **Automatic Symbol Generation (ASG)**

Automatic symbol generation assists in the creation of symbols. The quickest way to automatically create a symbol is from another cellview. Creating a symbol from an existing cellview also ensures that the pin properties will match between the cellviews. Other advantages to ASG are the automatic creation of symbol parameters from hierarchical variables in the schematic and the creation of CDF for the cell.

### **Symbol Generation**

#### Design—Create Cellview—From Cellview

|            |         | C            | ellvie | w From Cellvie   | W       |            |

|------------|---------|--------------|--------|------------------|---------|------------|

| ОК         | Cancel  | Defaults     | Apply  |                  |         | Help       |

| Library N  | ame     | mylib        |        |                  |         | Browse     |

| Cell Name  |         | amplifierį́  |        |                  |         |            |

| From Viev  | w Name  | schematic 🗆  |        | To View Name     | symbol  |            |

|            |         |              |        | Tool / Data Type | Compose | r-Symbol 📼 |

| Display C  | ellview | <del>\</del> |        |                  |         |            |

| Edit Optio | ons     | <b>~</b>     |        |                  |         |            |

This form opens with only the top portion, press these buttons to extend the symbol generation capabilities of the form.

Select a symbol generation template, other than the cdsinit entry.

Select symbol generation attributes to control the symbol drawing.

Select Apply or OK

|        | Symbol Generation Options                                                                                                     |       |  |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|

|        | OK Cancel Apply                                                                                                               | Help  |  |  |  |  |

|        | Library Name Cell Name View Name                                                                                              |       |  |  |  |  |

|        | myliki amplifieri symboli                                                                                                     |       |  |  |  |  |

|        | Pin Specifications Attri                                                                                                      | butes |  |  |  |  |

|        | Left Pins inm inp [                                                                                                           | List  |  |  |  |  |

|        | Right Pins Out 1                                                                                                              | List  |  |  |  |  |

|        | Top Pins                                                                                                                      | List  |  |  |  |  |

|        | Bottom Pins iref [                                                                                                            | List  |  |  |  |  |

|        | Load/Save Edit Attributes Edit Labels Edit Properties                                                                         | s 🗆   |  |  |  |  |

| ate, 🔶 | Load analog :ec/445/tools.sun4v/dfII/samples/symbolGen/artist                                                                 | .tsġ  |  |  |  |  |

|        | Library Name Cell Name View Name                                                                                              |       |  |  |  |  |

| es 🔶   | Symbol Attributes         Pin Spacing       0.125         Height       0         Stub Length       0.25         Width       0 |       |  |  |  |  |

|        | Reverse Pin Order                                                                                                             |       |  |  |  |  |

#### **Symbol Generation**

Bring up ASG from the schematic window. A template file will be used for the symbol creation. There are different symbol template files for different tools in the Design Framework II environment.

To make sure the *analog* symbol generation template is used in your design, put the following command in your *.cdsinit* file:

```

schSetEnv( "tsgTemplateType" "analog" )

```

Note: Failure to set this will result in a digital symbol generation.

Notice that the From View Name and To View Name fields can be modified in the Cellview from Cellview form. This provides a way to create other views, such as *behavioral* or *ahdl* from your schematics.

Interpreted labels on the symbol act as "placeholders" for different types of information to be displayed in the schematic.

- *cdsTerm()* labels display pin names or the net names.

- *cdsParam()* labels display parameters of an instance.

- cdsName() labels display the instance or cell name.

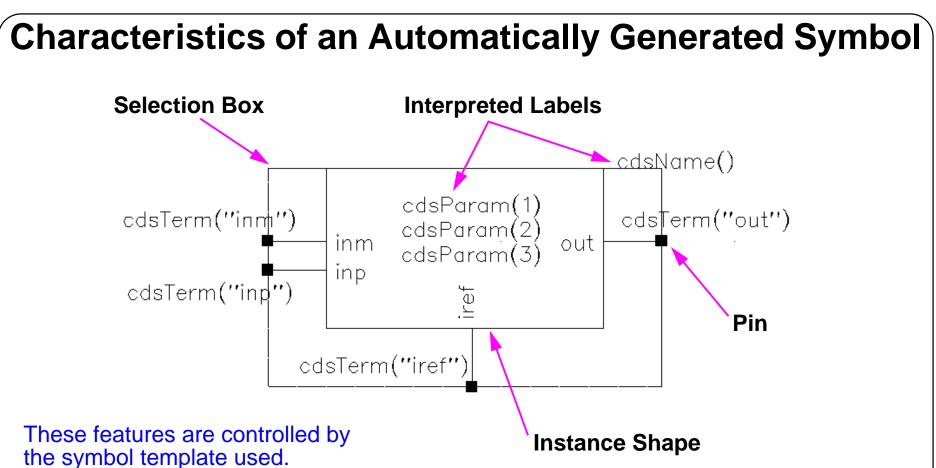

### **Characteristics of an Automatically Generated Symbol**

An automatically generated symbol cellview includes pins, a rectangular graphic and labels. It can be modified using the symbol editor.

**Note:** The generation depends on the symbol template selected either in .cdsinit or by the symbol generation form.

There is some control over how automatically generated symbols are drawn. By default, pins are placed at the left side of the symbol if their direction is input, at the right side of the symbol if their direction is output, and on top of the symbol if the direction is InputOutput. Options exist to change the pin appearance and order of the pins.

*Interpreted Labels* allow information to appear near the symbol after it is placed in another cellview. For the label generation template, the three label types are:

- *cdsTerm()* labels display pin names or the net names pins connect to.

- Each *cdsParam()* label can display a parameter of the instance. There can be multiples of this label.

- *cdsName()* labels display the instance or cell name.

All placeholder labels can be rearranged so that labels on instantiated instances are moved accordingly. These three labels have meaning in the Analog Design Environment. They display certain attributes, which are discussed later.

A selection box is drawn around the symbol and can be edited. It defines the symbol's selectable region after it is placed in another cellview.

# **Schematic Window Icons and Accelerator Keys**

The Composer Schematic software provides both icons and "Accelerator" keys to simplify schematic capture. The icons and Accelerator keys also reduce the time needed to capture and edit schematics.

- The icons appear on the left-hand side of the schematic editing window.

- An icon is activated by using a left click over the icon.

- Accelerator keys are activated by pressing specified keys on the keyboard.

- Accelerator keys are sometimes referred to as bindkeys.

#### **Schematic Window Icons and Accelerator Keys**

### **Composer Command Summary**

| COMMAND:            | bindkey | Mouse Sequence:             | icon? |

|---------------------|---------|-----------------------------|-------|

| Add Component       | i       | Add — Instance              | yes   |

| Select Component(s) | LMB     | left click, or drag LMB     | J     |

| Сору                | C       | Edit — Copy                 | yes   |

| Delete              | Del     | Edit — Delete               | yes   |

| Move                | m       | Edit — Move                 | •     |

| Stretch             | Μ       | Edit — Stretch              | yes   |

| Rotate              | r       | Edit — Rotate               | •     |

| Repeat              |         | RMB                         | yes   |

| Modify Properties   | q       | Edit — Properties — Objects | yes   |

| Add Wire            | W       | Add — Wire                  | yes   |

| Add Wire Name       | I       | Add — Wire — Name           | yes   |

| Add Pin             | р       | Add — Pin                   | yes   |

| Undo                | u       | Edit — Undo                 | yes   |

| Redo                | U       | Edit — Redo                 |       |

## **Composer Command Summary**

| COMMAND:         | bindkey | Mouse sequence:                   | icon? |

|------------------|---------|-----------------------------------|-------|

| Zoom in by 2     | ]       | Window — Zoom — zoom in by 2      | yes   |

| Zoom out by 2    | Ι       | Window — Zoom — zoom out by 2     | yes   |

| Zoom in          | Z       | Window — Zoom — Zoom in           |       |

| Zoom out         | Ζ       | shift — RMB                       |       |

| Fit              | f       | Window — Fit                      |       |

| Redraw           | f 6     | Window — Redraw                   |       |

| Check and Save   | X       | Design — Check and Save           | yes   |

| Save As          | ^s      | Design — Save As                  |       |

| Delete Marker    | ^g      | Check — Delete Marker             |       |

| Descend Edit     | Е       | Design — Hierarchy — Descend Edit |       |

| Return           | ^e      | Design — Hierarchy — Return       |       |

| Delete All Edits |         | Design — Discard Edits            |       |

| Close            |         | Window — Close                    |       |

# Bindkeys

Many of the schematic capture commands have alternative ways to be invoked.

- 1. A command sequence such as: Edit—Properties—Objects

- 2. An icon such as:

- 3. A bindkey such as **q**

Bindkeys include the following features:

- Speed up schematic capture flow

- Default set of functions with installation

- Functions may be customized

- Full set of may be viewed or changed using **Options—Bindkeys** in the CIW

## **Bindkeys**

Bindkeys simplify the schematic capture flow. A default set of Accelerator keys is provided; however, the keys are programmable. To view the key settings and the corresponding SKILL syntax, select in the CIW: Options—Bindkeys. A "Key or Mouse Binding Window" appears. This window shows bindkeys for the schematic editor and other tools. In the Application Type Prefix cyclic field select *schematic*.

Then select the Show Bind Keys button. The Schematic Bindkeys window will appear.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Schematics Bindkeys                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| File R                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Help 11  |

| list(" <key>8"<br/>list("<key>9"<br/>list("<key>9"<br/>list("<key>BackSpace"<br/>list("<key>Down"<br/>list("<key>Escape"<br/>list("<key>F1"<br/>list("<key>F3"<br/>list("<key>F4"<br/>list("<key>F6"<br/>list("<key>F6"<br/>list("<key>Left"<br/>list("<key>Left"<br/>list("<key>Up"<br/>list("<key>Up"<br/>list("<key>["<br/>list("<key>]"</key></key></key></key></key></key></key></key></key></key></key></key></key></key></key></key></key> | <pre>"schHiHiliteLabel(\"instance\" \"on\")") "geAddNetProbe()") "schHiDelete()" "deletePoint()") ;EF "schHiDelete()") "geScroll(nil \"s\" nil)") "" "cancelEnterFun()") ;EF "hiHelp('window deGetAppInfo(deGetEditViewType(hiGetCurrentWindow()))-&gt;ap nil "hiToggleEnterForm()") ;EF "geTogglePartialSelect()") "hiRedraw()" "geScroll(nil \"w\" nil)") "geScroll(nil \"w\" nil)") "geScroll(nil \"w\" nil)") "geScroll(nil \"n\" nil)") "niZoomRelativeScale(getCurrentWindow() 1,25)")</pre> | opName)" |

| list(" <key>a"<br/>list("<key>b"<br/>⊡_</key></key>                                                                                                                                                                                                                                                                                                                                                                                               | "geSingleSelectPoint()")<br>"schHiCreateBlockInst()")                                                                                                                                                                                                                                                                                                                                                                                                                                              | <br>     |

Note: This is a partial list. To view all bindkeys use scroll bar.

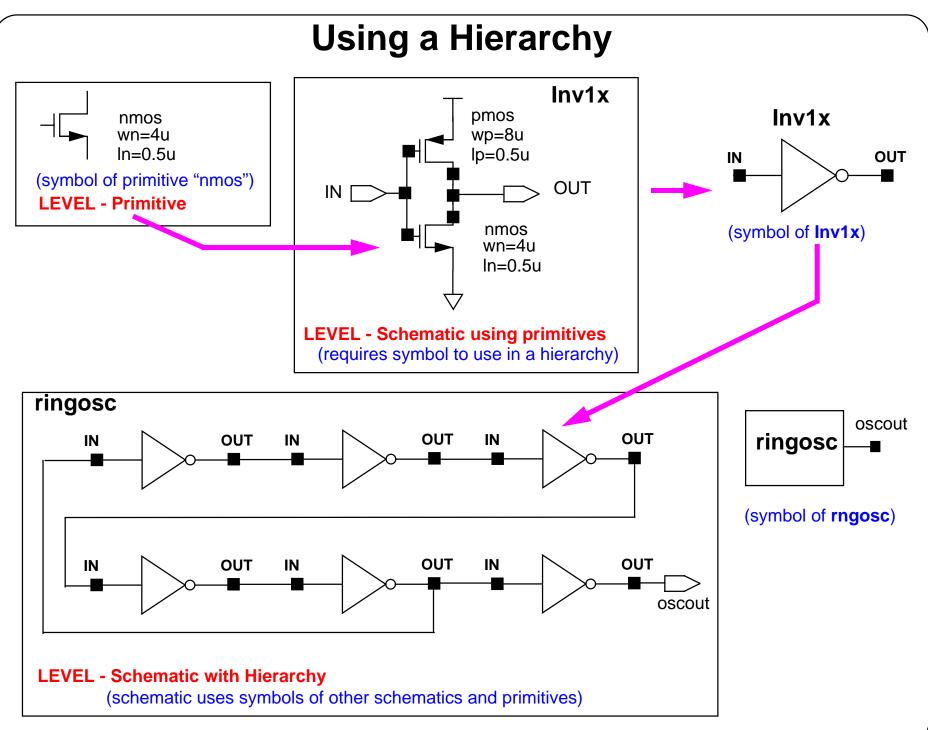

## Using a Hierarchy

A hierarchy is the design data of a complex system organized into simple and manageable data at different levels. A hierarchy simplifies the complex structure of a system. It often reduces the storage requirements for the data. It also simplifies and reduces the time to design the system.

Primitives are the basic design elements and exist at the bottom of the hierarchy. The design does not descend below this level. A schematic may consist entirely of primitives. Such a schematic is also referred to as a flat schematic or a primitive-level schematic. For large systems, for example a 16-bit analog-to-digital converter, it is difficult capture the design with a flat schematic.

A design of a complex system can consist entirely of a single schematic. The flat schematic can be simulated by including sources for power and stimulus. A design using only a flat schematic (without hierarchy) is inefficient when repeated structures are used. Such a schematic becomes difficult to manage as the circuit complexity increases.

A schematic can use symbols of primitives and symbols for other schematics. Such a schematic is more efficient to design repeated structures and complex systems. This use of symbols to represent schematics continues to higher and higher levels of hierarchy until the TOP level of the design is reached.

A symbol for a schematic view is only required when that schematic is used within a hierarchy.

Lab 2-1 Schematic Entry

Lab 2-2 Symbol Creation

Lab 2-3 Building the Supply Circuit

Lab 2-4 Building the ampTest Design

#### Labs

## Lab Reference Material: Mouse Buttons

| Left Mouse Butt    | on—Select and Deselect        | Middle Mouse E                    | Button                      |  |

|--------------------|-------------------------------|-----------------------------------|-----------------------------|--|

| Click Select point |                               | Pop-Up Menus                      |                             |  |

| Double click       | Extend select                 | Click                             | Pop-up menus                |  |

| Shift-click        | Select point (add)            | (EF)                              | Pop-up menus                |  |

| Control-click      | Deselect point                | Right Mouse Bu<br>Repeat, Zoom, C |                             |  |

| Draw through       | Select box or Direct<br>Edit* | Click                             | Repeat last command         |  |

| Shift draw         | Select box (add) or           | Draw through                      | Zoom in                     |  |

| through            | Direct Edit*                  | Shift draw                        | Zoom out                    |  |

| Control draw       | Deselect box or               | through                           |                             |  |

| through            | Direct Edit*                  | (EF)                              | Command options             |  |

| (EF)               | Add point                     |                                   | (command-specific bindings) |  |

**Note:** EF (Enter Function) bindkeys used within an active command. \*Direct Edit applies only when over object.

#### Lab Reference Material: Mouse Buttons

## Module 3: Analog Simulation

#### **Topics in this module**

- Overview of the simulation environment

- Setting up the simulation environment

- Model files

- Design variables

- Choosing analyses

- Netlisting

- Running simulation

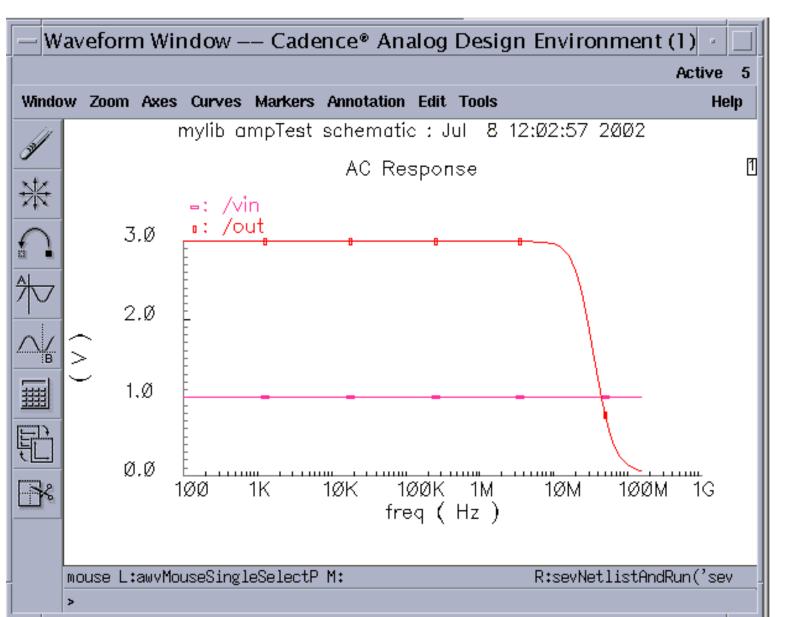

- Viewing simulation results with the Waveform display tool

- Saving simulator sessions

#### **Terms and Definitions**

| analyses field    | A text field in the simulation widow indicating selected analyses.       |

|-------------------|--------------------------------------------------------------------------|

| output field      | A text field in the simulation widow indicating selected output.         |

| Spectre           | A Cadence simulation tool for simulating analog circuits.                |

| simulator host    | Software tool such as Spectre, cdsSpice, etc. to be used for simulation. |

| model library     | A text file having model description used by the simulator host.         |

| stimulus template | A user interface used to establish signals used in simulation.           |

| netlist           | A textual description of a schematic used by the simulator host.         |

| Waveform Window   | A graphical interface used to plot simulation data.                      |

| direct plot       | User command used for 'special' plots to the Waveform Window.            |

| annotating        | Process of displaying data back to another window or schematic.          |

| label display     | A label attached to a component for displaying information.              |

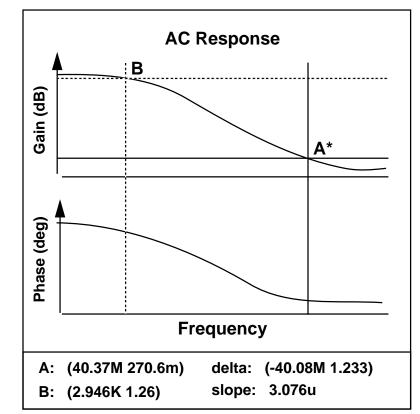

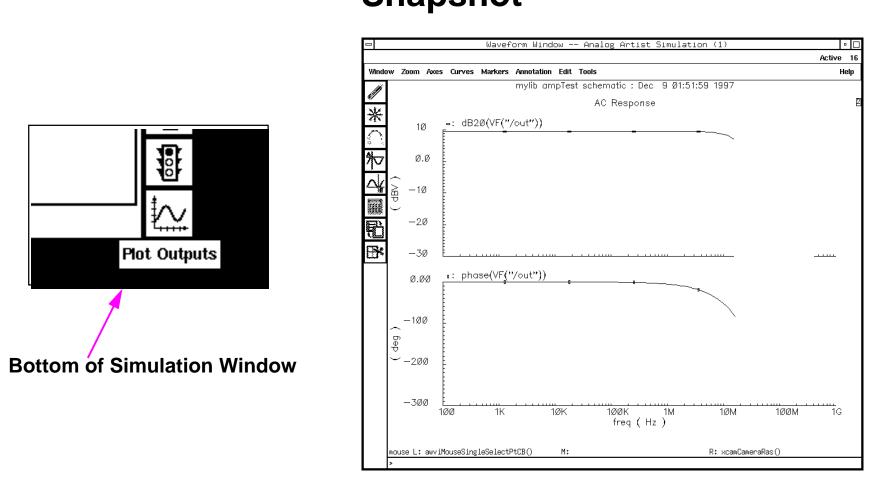

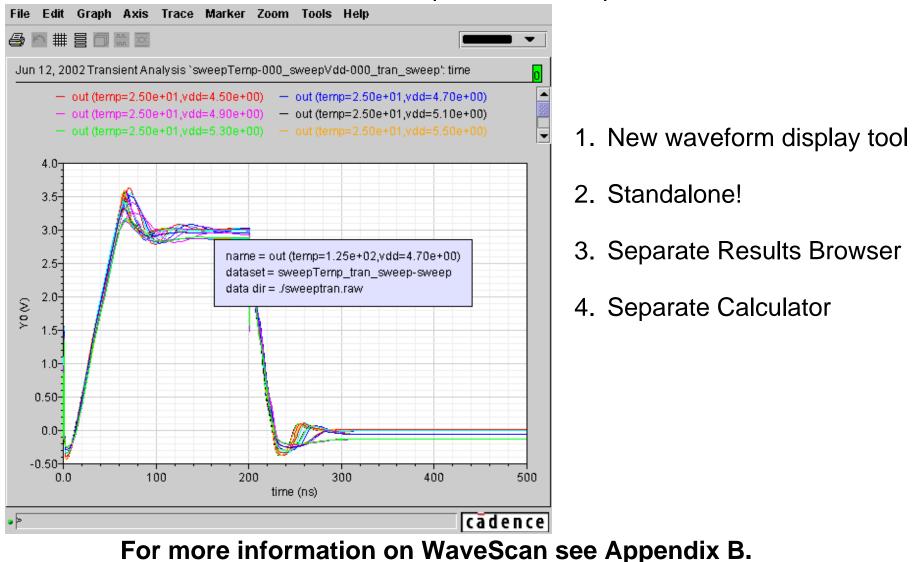

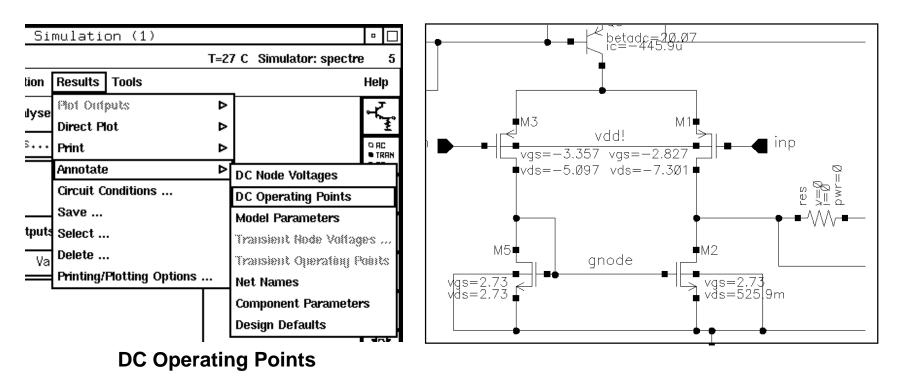

| snapshot          | A command to the Waveform Window to update intermediate results.         |

# **Overview of the Analog Design Environment**

The **Analog Design Environment** is a user-friendly graphical interface tool to set up, run, and evaluate analog circuit simulations:

## **Overview of the Analog Design Environment**

The Analog Design Environment is a software design tool the provides an easy way to set up, run, and evaluate analog circuit simulations. It provides a simple way to change the input file to run the next simulation. It provides access to the simulation output files to view waveforms, make waveform measurements, and evaluate expressions. Think of the Analog Design Environment as your "control panel".

Use the Analog Design Environment to:

- Setup simulations

- Netlist the circuit

- Run the simulation

- Evaluate the simulation results

####

The Analog Design Environment is often referred to as the **"simulation environment"** or the **"simulation window"**.

Note: It was also known in prior releases as "Analog Artist" and sometimes as "Artist".

Analog Simulation

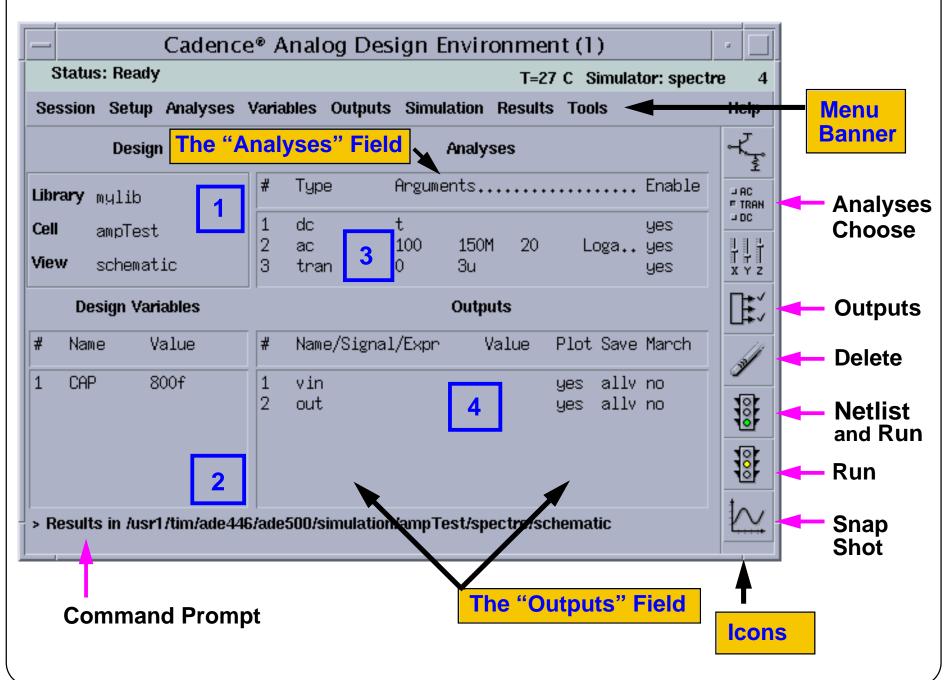

## **Important Features of the Simulation Window**

#### **Important Features of the Simulation Window**

The diagram shows the Analog Design Environment window. The simulation window is annotated with notes used to describe the important features.